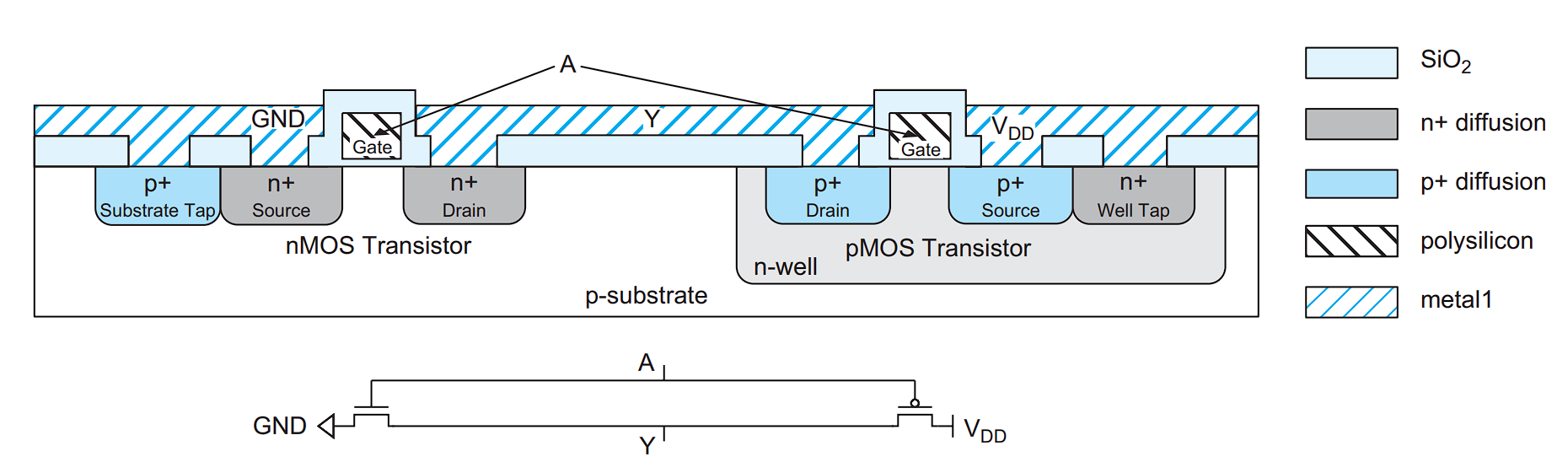

反相器组成

以如何制造一个反相器为例。

包含一对 nMOS 和 pMOS 晶体管。

晶体管包括

- 高掺杂的源极,漏极

- 高掺杂的

多晶硅栅极(polysilicon gate) 与一层超薄二氧化硅绝缘栅氧(gate oxide) - 一层覆盖的厚二氧化硅绝缘

场氧(field oxide) ,上有蚀刻的接触孔(contact)

一些布线

- 两晶体管的多晶硅栅极接在一起构成输入 A

- nMOS 源极接金属地线,pMOS 源极接金属 $V_{DD}$ 线

- 两晶体管的漏极接在一起构成输出 Y

- 为防止 p 衬底与 n 掺杂源漏极构成 PN 结正向偏置,将 p 衬底通过重掺杂

衬底接触(substrate tap) 接地;同理,将 n 井通过重掺杂的井接触(well tap) 接 $V_{DD}$

金属与轻掺杂半导体间会形成肖特基二极管(Schottky diode),只允许电流单向流动。为使衬底与井接入电压避免 PN 结正向偏置,需要专门创造出一个重掺杂的区域,其与金属能形成良好的欧姆接触(Ohmic contact),从而为双向电流提供低电阻通路。这个区域就称为接触(taps)。

制造工艺

可以看看 这个视频。

芯片是经一系列步骤「印」上去的,因此成本与面积而非晶体管数量有关。

晶圆(silicon wafer)和晶圆厂(fabs)。

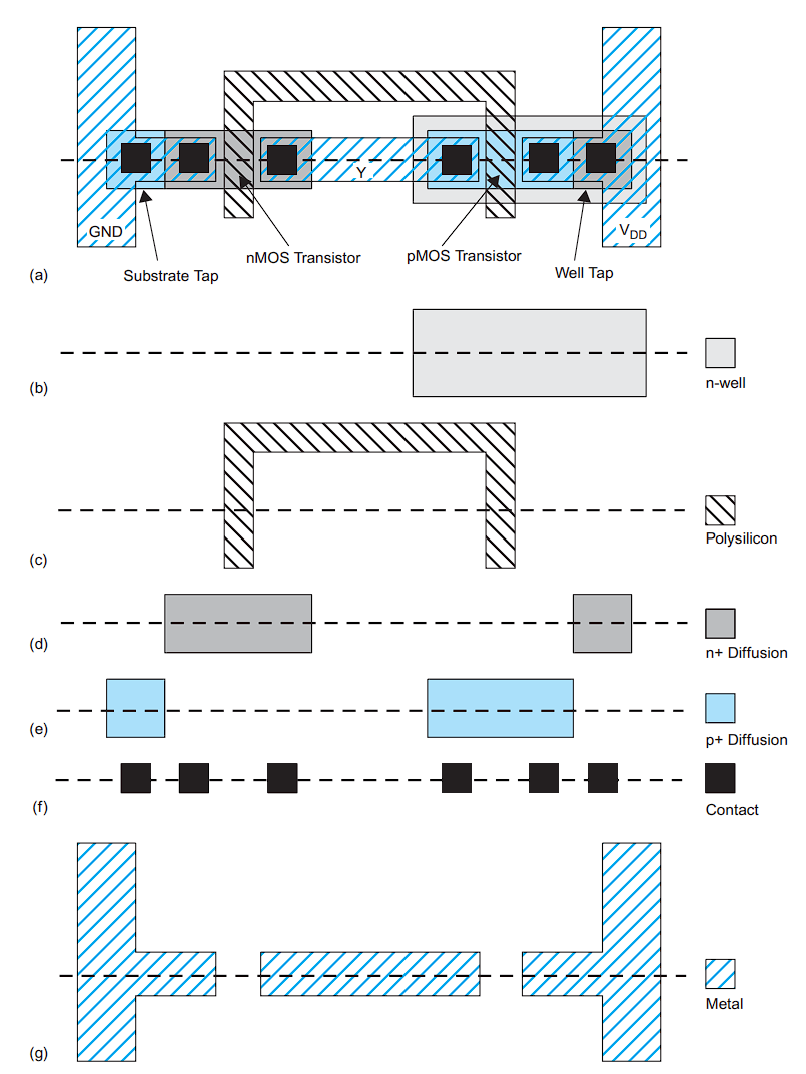

n 井的植入

第一步:氧化 Oxidation晶圆在氧化炉中与水或氧气反应,生成二氧化硅层。

第二步:光刻 Lithography在晶圆上旋涂(spin)正性有机光刻胶(photoresist),其受光照处会软化。

用 n 井掩模版对光刻胶曝光(exposed through the n-well mask),去除(strip off)软化的光刻胶,露出对应位置的氧化层。

第三步:蚀刻 Etching用氢氟酸(hydrofluoric acid)蚀刻未被光刻胶保护的氧化层,然后使用食人鱼蚀刻液(piranha etch,多种酸的混合液)去除剩余的光刻胶。

第四步 引入掺杂原子井将形成在衬底未被氧化层覆盖的位置。

有两种方法引入掺杂原子:

扩散(diffusion) :将晶圆放入含有掺杂剂气体的炉管中加热,掺杂原子会向衬底内部扩散离子注入(ion implantation) :掺杂离子在电场中被加速,被轰击注入(blasted into)衬底

由于横向扩散(lateral diffusion),井的宽度会比氧化层开口稍宽些。

形成井后,使用氢氟酸将氧化层去除,得到了带有 n 井的裸晶圆。

多晶硅栅极的植入

第一步:氧化

在炉管中生长出极薄的二氧化硅栅氧(gate oxide)层。

第二步:化学气相沉积(Chemical Vapor Decomposition,CVD)将晶圆至于充满硅烷气体(Silane gas)的炉管中加热,生长出多晶硅层。

第三步:重掺杂

多晶硅层被重掺杂,称为导电性较好的导体。

第四 ~ N 步:同上,用光刻胶配合多晶硅掩膜版对晶圆进行图形化处理(patterned),得到带有薄栅氧的多晶硅栅极的晶圆。

引入 n 与 p 扩散区域

n 扩散区域包括 p 衬底中的两个 n 掺杂的源极区和漏极区与一个 n 井中的井接触。

第「一」步:类似的,使用氧化与掩膜暴露出需要引入掺杂剂的区域。

第二步:引入掺杂原子:

- 虽常用离子注入,但按传统仍将其称为

n 扩散(n-diffusion) 自对准(self-aligned)工艺 :已形成的多晶硅栅极会阻挡掺杂进入其下方,使得源漏之间会自动在栅下保留一段沟道区域;这一段无需在掩膜中精确的对准。

形成 n 扩散区域后去除氧化层。

第「三」步:用同样的步骤引入 p 扩散区域:n 井中两个 p 掺杂的源漏区和一个 p 衬底中的衬底接触。

场氧,接触孔与金属化

第一步:生长厚厚的场氧(field oxide)层使晶圆与之后的金属层绝缘。

第「二」步:在场氧层上使用接触孔掩膜进行图形化,使得多晶硅或扩散区能够通过接触孔(contact cuts)与金属相连接。

第三步:金属化- 在整个晶圆上

溅镀(sputtering) 铝(铝也会填充接触孔) - 在金属层上使用金属掩膜进行图形化,使用等离子体蚀刻(plasma etching)掉多余的金属,留下导线(wires)所在的区域

一种物理气相沉积技术,通过将铝轰击成蒸气,使其均匀覆盖在晶圆表面。