布局设计规则

如何在掩膜上画布局?

工艺节点的特征尺寸(feature size)$f$:晶体管的最小沟道长度,即源漏极间距离。

$\lambda$ 规则:$\lambda=f/2$,并且所有布局中的间距都用 $k\lambda$ 表示 => 布局可缩放。

MOS 晶体管尺寸常用 Width $/$ Length 定义:宽度 $W$ 是沟道宽度,长度 $L$ 是沟道长度,所以 $L=f=2\lambda$。

- nMOS 最小尺寸常取 $4\lambda/2\lambda$

- 由于空穴的移动速度比电子慢,为提供相同的电流,pMOS 必须做得更宽:常取 $8\lambda/2\lambda$

门布局与棒图

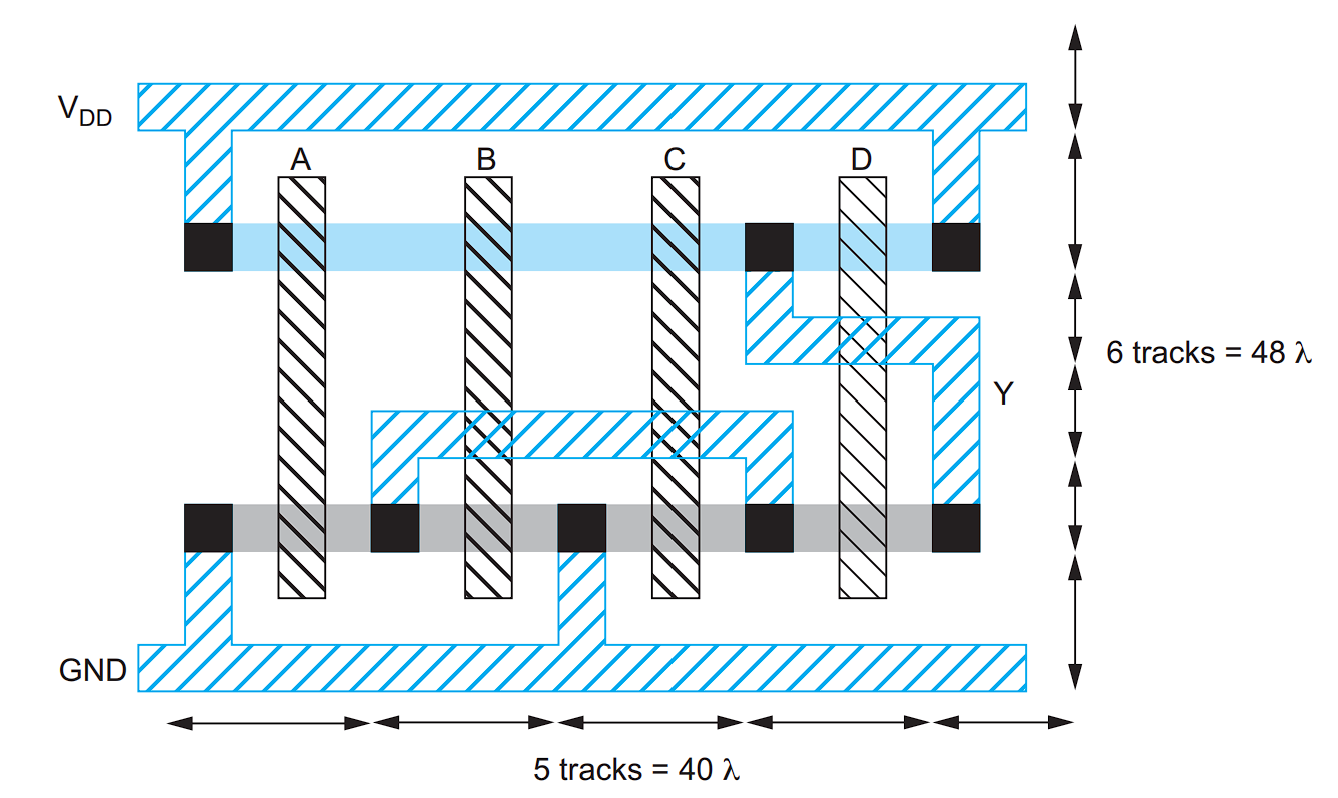

在许多标准单元(standard cells)中采用的是这样的门布局(gate layout):

由上到下,四条水平条带(strip):

- 金属电源线 VDD

- p 扩散区 pDiff

- n 扩散区 nDiff

- 金属地线 GND(电源线与地线又称为供电轨 power rail)

单元内部的金属连线用于连接晶体管。

布局草图:棒图(stick diagram),无需按比例绘制。

面积估算

给定一个布局草图或棒图,作面积估算。

一条布线轨道(routing/wiring track)占 $4\lambda$ 宽,与相邻轨道也需要留出 $4\lambda$ 的间距:因此一个

晶体管(所在的扩散区)也会占用一条布线轨道。

井间距(well spacing)要求井区必须以 $6\lambda$ 的间距包围晶体管。这意味着 nDiff 与 pDiff 之间需要预留至少 $2\times 6\lambda=12\lambda$ 的间距。$12\lambda$ 减去一条晶体管的轨道间距 $4\lambda$ 恰好等于一节距 $8\lambda$。这意味着 nDiff 与 pDiff 之间若有 $n$ 条金属布线轨道,需占用 $\max(n, 1)$ 个节距。

面积估算一例:

水平节距:VDD x1, pDiff x1, (pDiff, nDiff) x2, nDiff x1, GND x1 => $6\times 8\lambda=48\lambda$

垂直节距:metal wires x5 => $5\times 8\lambda=40\lambda$

因此面积估算为 $48\lambda\times50\lambda=2400\lambda^2$

物理设计

物理设计(physical design)指的是把逻辑设计(logic design)如网表等映射为满足时序,功耗,面积与可制造性约束等的具体布局实现过程。

floorplan 决定各功能块的面积与相对位置,可与逻辑决策反复迭代

- 面积:pad-limited 与 core-limited

- 片上结构(on-chip structures):随机逻辑(random logic),数据通路(datapaths),阵列结构(arrays),模拟电路(analog),输入/输出

标准单元(standard cells)与库:统一尺寸与布局,利于自动综合与布局布线(automatic synthesis, place & route)。

snap-together 单元:手工将一部分常用连线做进单元里,减少外部布线面积。这需要相邻单元对接时连线也能连在一起。通过节距匹配(pitch matching)实现无缝拼接。

slice plan:用布线轨道(wiring tracks)标注每个单元宽度及信号跨越情况,作为一种早期的物理可行性验证工具,在正式布局前估算面积与拥塞。

面积估算。

其他

设计验证(design verification):检查布局的设计。

- 版图 vs 原理图工具(Layout vs. Schematic, LVS tools)

- 设计规则检查(Design Rule Check, DRC)

- 电气规则检查(Electrical Rule Check, ERC)

生产,封装(packaging)与测试

- 出带(tapeout),流片(fabrication run)

- 良率(yield):一片晶圆上有多少比例的芯片功能正常

- 单颗芯片成本:晶圆成本 $/$(每片晶圆的芯片数 $\times$ 良率)