延迟的定义

当输入发生变化时,输出至少在污染延迟(contamination delay) 内保持原值,并至多在传播延迟(propagation delay) 内变为新的值。有时还会区分输出的上升延迟与下降延迟。

- 污染延迟:输入跨过 50% 到输出跨过 50% 所需的最小时间 min-time

- 传播延迟:输入跨过 50% 到输出跨过 50% 所需的最大时间 max-time

污染延迟远小于传播延迟,所以当单独提到延迟时,常指的是传播延迟。

精确的延迟评估:建模后解复杂的微分方程,SPICE 电路仿真等。

本节介绍的是 RC 延迟模型,它用晶体管开关(switching)过程中平均的电阻与电容来近似非线性的 I-V 和 C-V 特性。它难以细致的模拟电路行为(比如预测某时刻电流的值,这还是得回到肖特基一阶晶体管模型),但能足够准确的估算延迟。

有效电阻

把晶体管视作一个与电阻串联的开关,它的有效电阻(effective R)是开关过程中各个时刻 $V_{ds}/I_{ds}$ 的平均值。规定单位 nMOS 晶体管($4\lambda/2\lambda$)的有效电阻为 $R$。

所以有一系列结论:

- 单位 pMOS 晶体管的有效电阻为 $2R$(空穴迁移率低)

- 宽度为单位晶体管 $k$ 倍的 nMOS 晶体管的有效电阻为 $R/k$

- 串联晶体管的总电阻等于各晶体管电阻之和

- 并联晶体管的总电阻倒数等于各晶体管电阻倒数之和

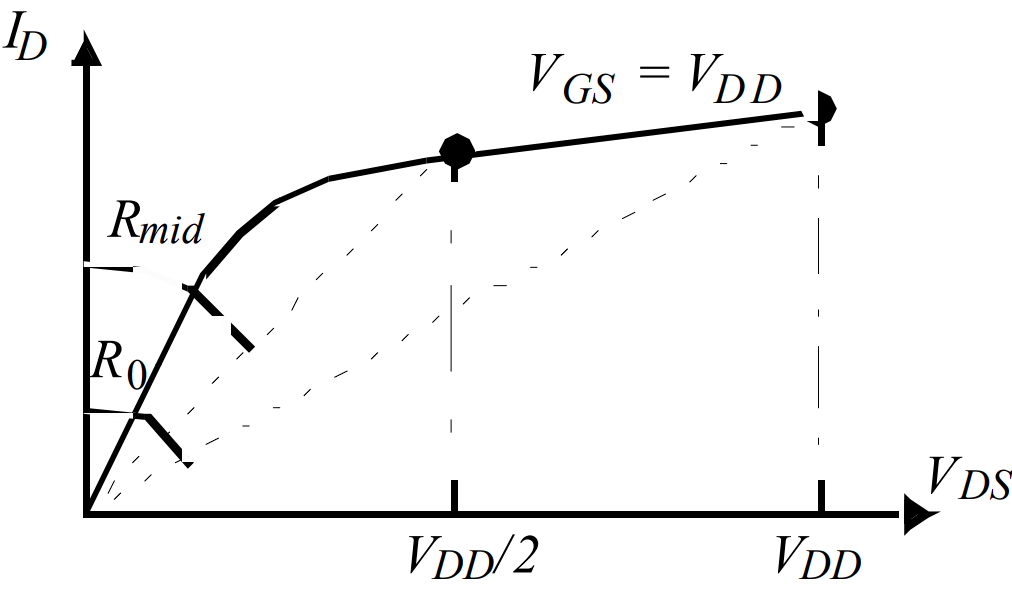

以计算一个理想反相器的有效导通电阻为例:给一个阶跃上升信号 $V_{GS}=V_{DD}$,导通的是 nMOS 晶体管:

输出电压从 $V_{DD}$ 开始,线性下降到 $V_{DD}/2$ 时反相器发生翻转,再非线性下降到 $0$。一般而言,开关过程指的是输出逻辑电平切换的电压变化区间,即 $V_{out}:V_{DD}\to 0$;但因为传播延迟只计算到输出的 50% 切换点,所以常关注 $V_{out}:V_{DD}\to V_{DD}/2$。

由于开关过程中电压是随时间线性变化的,全程的平均值等于首尾的平均值,所以有:

$$

R_{eq}=\frac{1}{2}(\frac{V_{DD}}{I_{dsat}(1+\lambda V_{DD})}+\frac{V_{DD}/2}{I_{dsat}(1+\lambda V_{DD}/2)})

$$

这里的 $(1+\lambda V_{DD})$ 是沟道长度调制带来的影响。

栅电容与扩散电容

除开关与有效电阻外,电容(栅电容与源/漏扩散电容)也是晶体管的重要组分。规定单位 nMOS 晶体管的栅电容为 $C$,根据之前的假设(CV 特性:极体电容),扩散电容也为 $C$。

栅电容与沟道长,宽有关,扩散电容与源漏极尺寸有关。

- 单位 pMOS 的栅电容为 $C$,扩散电容为 $C$

- 宽度为单位晶体管 $k$ 倍的晶体管的栅电容为 $kC$,扩散电容为 $kC$

- 长度为单位晶体管 $k$ 倍的晶体管的栅电容为 $kC$,扩散电容为 $C$

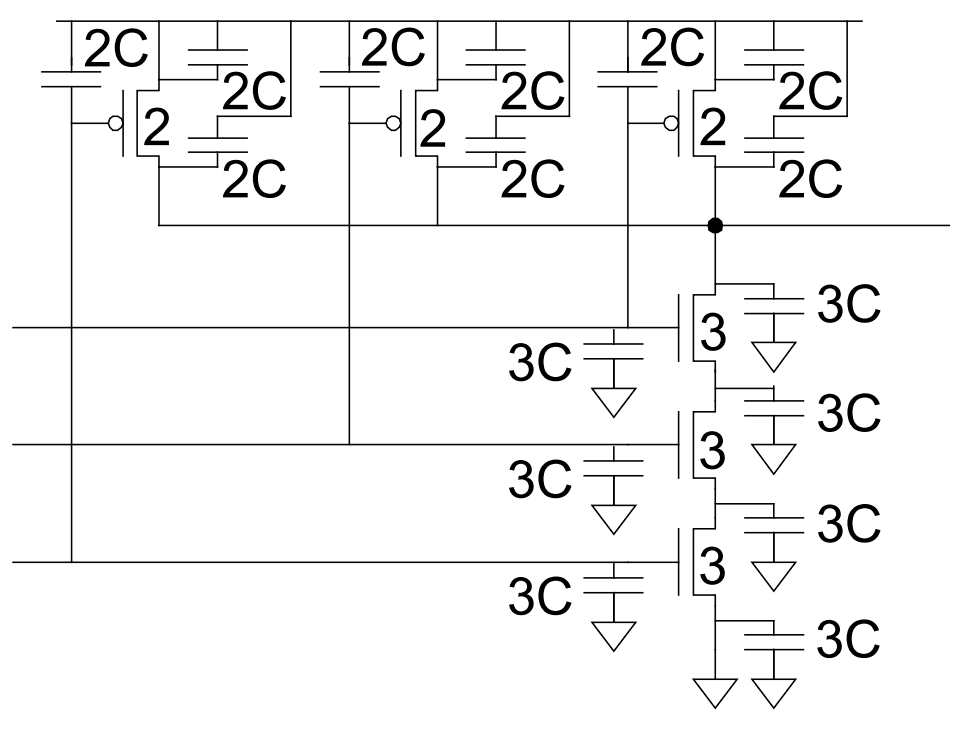

注意到上图中串联 nMOS 晶体管有源漏扩散电容共用;可见一个好的布局能够削减延迟。

去除非开关(noncapacitance)电容(被 GND 与 VDD 短路的源扩散电容),合并相同路径上的开关电容(三个输入路径上的栅电容分别合并,输出路径上的漏扩散电容合并),得到:

RC 延迟模型:一例

若晶体管有效电阻为 $R$,其输出节点上的总电容为 $C$,那么传播延迟可近似为 $t_{pd}=RC$。

RC 延迟模型把晶体管的开关行为视作一个电阻给电容充放电。以放电(nMOS 导通)为例,根据电容电流 $=$ 电阻电流,有:

$$

C_{load}\frac{d_{out}}{dt}=-\frac{V_{out}}{R}

$$

解得:

$$

V_{out}(t)=V_0 e^{-t/RC}

$$

当输出降至 50% 时,有:

$$

\frac{V_{DD}}{2}=V_0 e^{-t/RC}

$$

约去 $V_{DD}$,取对数,近似得到:

$$

T_{50\%}\approx 0.69 RC \approx RC

$$

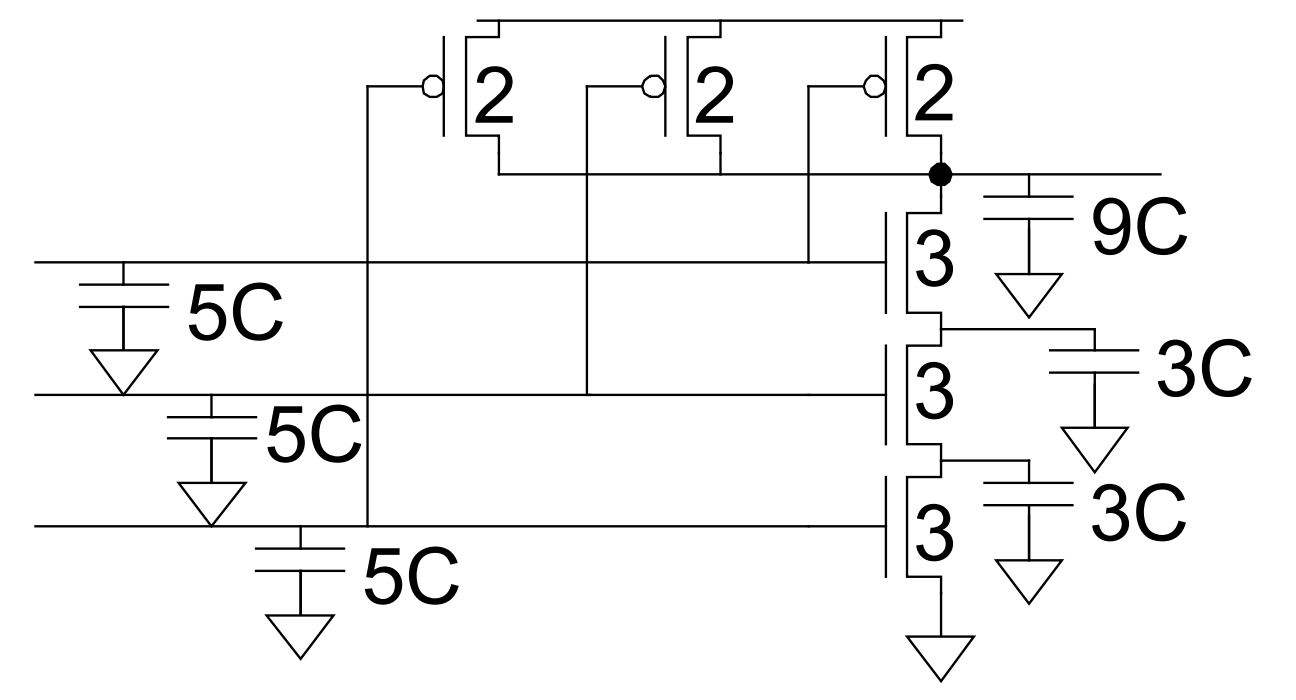

一个例子,给阶跃上升信号,用 RC 延迟模型计算一个扇出为 1,nMOS 与 pMOS 宽度比为 $1:2$ 的反相器(FO1)延迟:

扇出指的是一个门的输出接了多少个门的输入。

关注输出节点 $Y$:

- 阶跃信号下 nMOS 导通,有效电阻为 $R$

- 本级门的寄生电容:nMOS 漏扩散电容 $C$ 与 pMOS 漏扩散电容 $2C$

- 次级门的负载电容:nMOS 栅电容 $C$ 与 pMOS 栅电容 $2C$

所以输出节点上的总电容为 $C_{load}=6C$,有效电阻为 $R$,延迟为 $6RC$。

Elmore 延迟

如果一个电路能表示成一颗 RC 树(无回路,单一根节点,所有电容接地的 RC 电路)的形式,就可以用 Elmore 模型估计从根节点发生开关变化,到某一个叶节点(分支末端电容)发生变化的一阶常数延迟。

源指的是施加在 RC 树上的信号,根节点则是信号传播(propagate)的起点。以反相器为例,pMOS 导通,VDD 把 RC 树拉向高电平,因此源是阶跃上升信号,VDD 是根节点;nMOS 导通,GND 把 RC 树拉向低电平,因此源是阶跃下降信号,GND 是根节点。

计算方法:对树中每个叶节点 $k$ 求和,把该节点上的电容 $C_k$ 乘以从根节点 $s$ 到该节点 $k$ 与从根节点 $s$ 到目标叶节点 $i$ 的共享路径上的等效电阻 $R_{ik}$。

$$

\tau_{Di}=\sum_{k=1}^N C_k [R_{ik}=R(\text{path}(s\to i)\cap \text{path}(s\to k))]

$$

长线(long wire)的 Elmore 延迟:$\tau_N=\sum_{i=1}^N R_i \sum_{j=i}^N C_j=\sum_{i=1}^N C_i \sum_{j=1}^i R_j$。把长线分成 $N$ 等段,单位段的电阻为 $r$,电容为 $c$,则有:

$$

\begin{aligned}

\tau_{DN}&=(\frac{L}{N})^2(rc+2rc+…+Nrc)\\

&=(rcL^2)\frac{N(N+1)}{2N^2}\\

&=RC\frac{N+1}{2N}\\

&=\frac{RC}{2} \quad \text{for large } N \\

&=\frac{rcL^2}{2}

\end{aligned}

$$

延迟与导线长度呈二次关系。

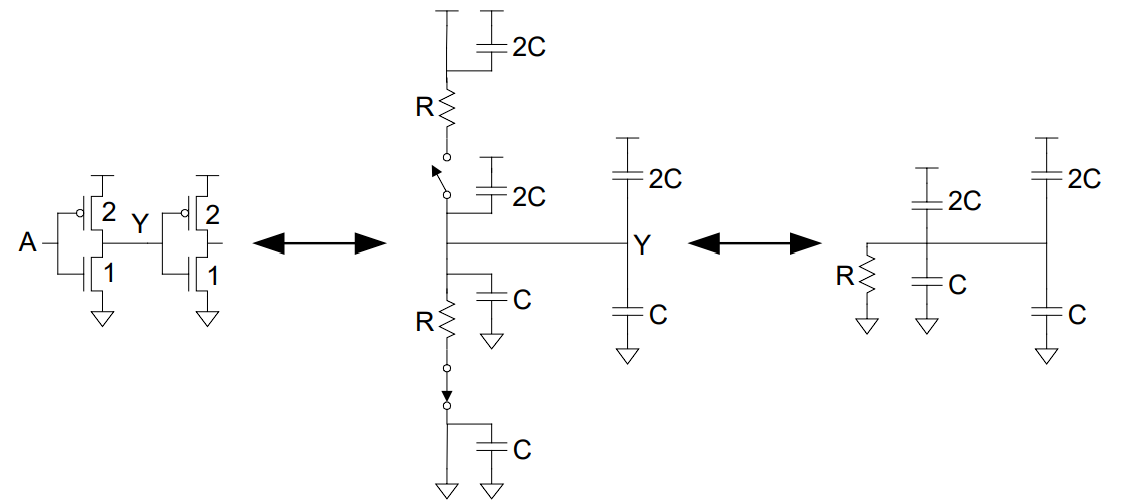

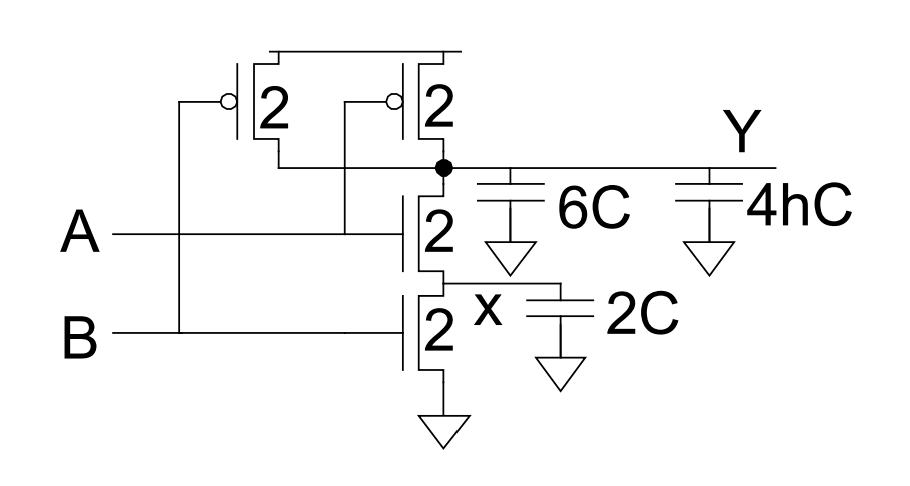

2 输入与非门:一例

评估一个 $h$ 扇出的 2 输入与非门的上升与下降传播延迟。

上升传播延迟:VDD 把 RC 树拉向高电平,将 VDD 视作根节点 $s$,$s\to Y$ 的路径上经过 pMOS(有效电阻 $R$),寄生电容 $6C$,负载电容 $4hC$,因此有 $t_{pdr}=(6+4h)RC$。

下降传播延迟:GND 把 RC 树拉向低电平,把 GND 视作根节点 $s$,$s\to Y$ 的路径上经过 nMOS1(有效电阻 $R/2$),寄生电容 $2C$,nMOS2(有效电阻 $R/2$),寄生电容 $6C$,负载电容 $4hC$,因此有 $t_{pdf}=(2C)R/2+(6C+4hC)(R/2+R/2)=(7+4h)RC$。