MOS 器件的模式

MOS 晶体管是一种多数载流子(majority-carrier)器件:源极与漏极之间导电沟道中的电流由施加在栅极上的电压控制。

以 nMOS 为例:

=> 累积(accumulation):栅极加负电压 $V_g<0$,因此栅极上带负电。体区中带正电的可移动空穴被吸引到栅极下方区域。

=> 耗尽(depletion):栅极加较小的正电压 $0<V_g<V_t$,因此栅极上带一定正电。体区中的空穴被排斥离开栅极下方区域,在栅下形成耗尽区(depletion region)。

=> 反型(inversion):栅极电压超过临界阈值 $V_g\geq V_t$,在栅极上吸引更多正电荷,空穴被进一步排斥,自由电子被吸引到栅下形成导电电子层,被称为反型层(inversion region)。

引入源极与漏极。

=> 截止(cutoff),或关断(OFF):栅源电压 $V_{gs}<V_t$。源极与体区均接地 $V_s=0$,以防止 p 型体区与两个 n 型源漏区组成的 PN 结正向偏置。

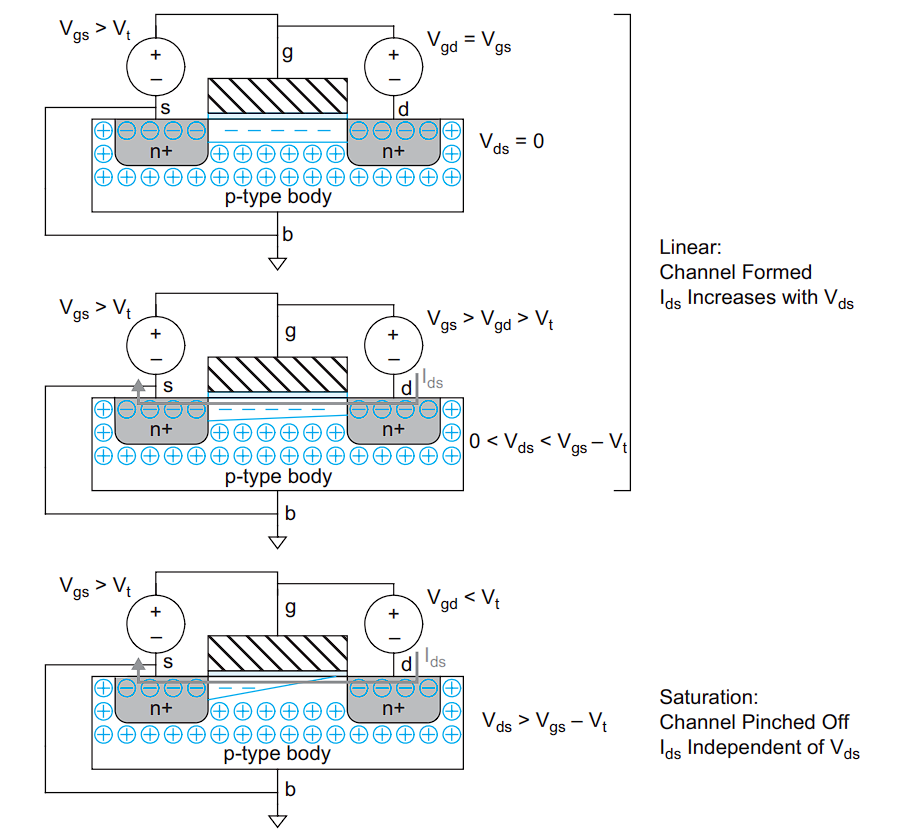

考虑给定某恒定栅压,使栅源电压 $V_{gs}\geq V_t$,源漏之间反型层构成沟道(channel),MOS 导通(ON)。

=> 线性(linear):漏极施加较小的电压造成漏源间电势差 $V_{ds}>0$,电流 $I_{ds}$ 形成,与 $V_{ds}$ 成正比。

=> 饱和(saturation):漏极电压增加至使 $V_{gd}=V_{gs}-V_{ds}<V_t$,沟道在近漏极 某处* 发生

沟道宽度与夹断点

长沟道 IV 特性

长沟道模型(long channel model),或肖特利模型(Shockley model)假设沟道长度足够长,横向电场(即源漏极之间的电场)相对较低。

电容器模型:栅极与反型层沟道形成一个电容器,两「极板」间电压差为 $V_{gc}$,其中阈值电压 $V_t$ 用于形成耗尽层,剩下的 $V_{gc}-V_t$ 用于实际堆出反型层。据电容定义式有:

$$

Q_{channel}=C_g(V_{gc}-V_t) \tag{1}

$$

因有源漏电势差,沟道电压处处不同。计算平均值:

$$

V_c=(V_s+V_d)/2=V_s+V_{ds}/2

$$

因有:

$$

V_{gc}=V_g-V_c=V_g-V_s-V_{ds}/2=V_{gs}-V_{ds}/2 \tag{2}

$$

若栅极长为 $L$,宽为 $W$,栅氧厚为 $t_{ox}$;兼有空气介电常数(permittivity)$\varepsilon_0$ 并二氧化硅介电常数 $k_{ox}$,则电容 $C_g$ 解为:

$$

C_g=k_{ox}\varepsilon_0\frac{WL}{t_{ox}}=\varepsilon_{ox}\frac{WL}{t_{ox}}=C_{ox}WL \tag{3}

$$

以式 $(2)$,$(3)$ 代回式 $(1)$,并记 $V_{gs}-V_t$ 为 $V_{GT}$:

$$

Q_{channel}=C_{ox}WL(V_{gs}-V_t-V_{ds}/2)=C_{ox}WL(V_{GT}-V_{ds}/2) \tag{4}

$$

沟道中载流子的平均速率与横向电场(即源漏间电场)成正比,比例常数为迁移率(mobility)$\mu$。低电场条件下 nMOS 晶体管中电子迁移率约为 $500\sim 700 \ cm^2/(V\cdot s)$。

$$

v=\mu E \tag{5}

$$

源漏间电场:

$$

E=\frac{V_{ds}}{L} \tag{6}

$$

则载流子经沟道由源至漏耗时:

$$

t=\frac{L}{v}=\frac{L}{\mu E} \tag{7}

$$

综合式 $(4)$,$(7)$,可计算源漏电流 $I_{ds}$:

$$

I_{ds}=\frac{Q_{channel}}{t}=\mu C_{ox}\frac{W}{L}(V_{GT}-V_{ds}/2)V_{ds}=\beta (V_{GT}-V_{ds}/2)V_{ds} \tag{8}

$$

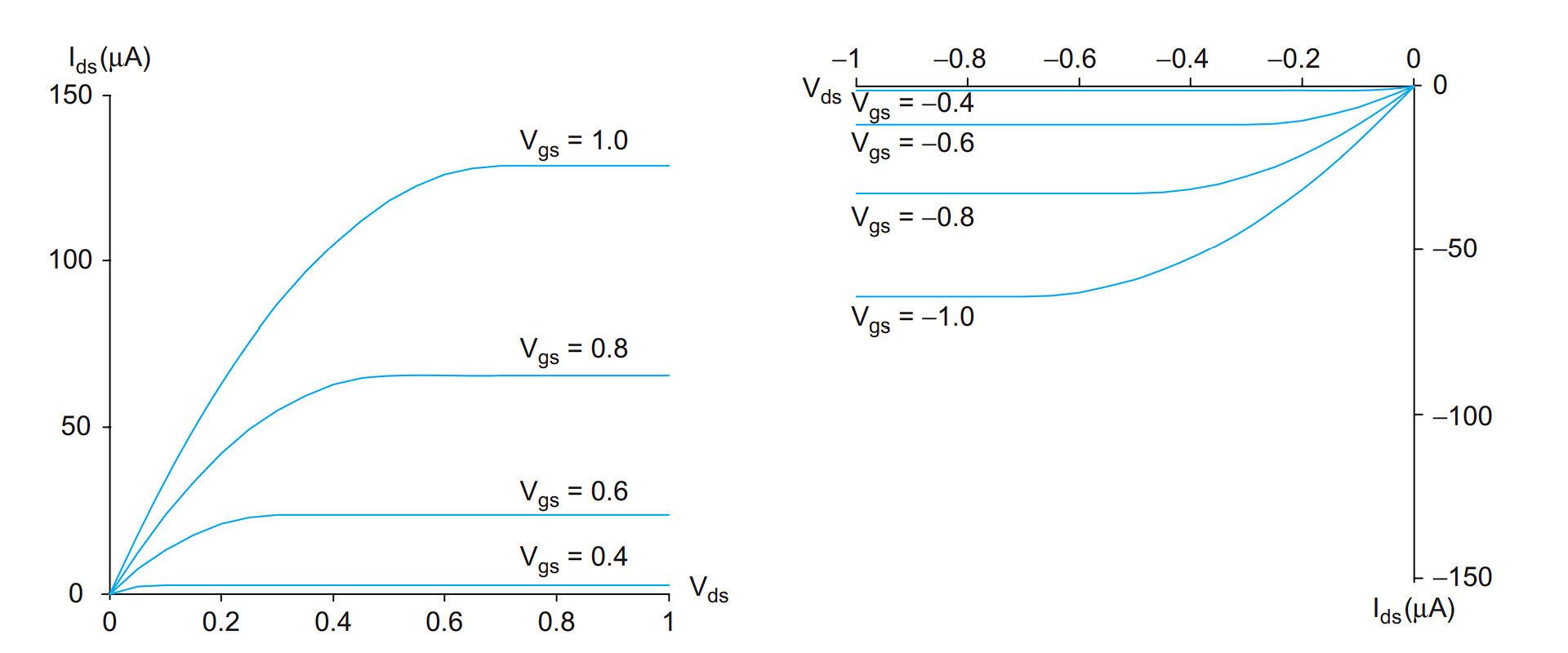

当 $V_t<V_{ds}<<V_{GT}$ 时,$I_{ds}$ 可近似的视为与 $V_{ds}$ 成正比,MOS 的表现近似于理想电阻,为线性状态。

当 $V_{ds}>V_{dsat}\equiv V_{GT}$(二次曲线 $-b/2a$)时,发生夹断,增大 $V_{ds}$ 不再影响电流,MOS 进入饱和状态。此时的有效电压为漏极饱和电压 $V_{dsat}$,将其代回 $(8)$ 得到饱和电流:

$$

I_{sat}=\frac{\beta}{2}V_{GT}^2

$$

所以有

$$

\begin{equation}

I_{ds} =

\begin{cases}

0, & V_{gs} < V_t \qquad &\text{Cutoff} \\

\beta\left(V_{GT}-\frac{V_{ds}}{2}\right)V_{ds},

& V_{ds} < V_{dsat} \qquad &\text{Linear} \\

\dfrac{\beta}{2}V_{GT}^{2},

& V_{ds} > V_{dsat} \qquad &\text{Saturation}

\end{cases}

\end{equation}

$$

不理想的 IV 表现

实际的 MOS 会出现各种与长沟道模型不符的不理想 IV 表现(nonideal IV effects)。

速度饱和(velocity saturation):高横向电场 $(V_{ds}/L)$ 下,载流子的速度不再与场强成正比,$(5)$ 失效 => 高漏压 $V_{ds}$ 下 $I_{ds}$ 低于预测值

移动力衰减(mobility degradation):高垂直电场 $(V_{gs}/t_{ox})$ 下,载流子更加分散 => 高栅压 $V_{gs}$ 下 $I_{ds}$ 低于预测值

沟道长度调制(channel length modulation):高漏压 $V_{ds}$ 下,漏极附近的耗尽层增大,沟道长度 $L$ 缩短 => 饱和电流 $I_{dstat}$ 随 $V_{ds}$ 的增加略微增加

非恒定的阈值 $V_t$:

- 体效应(body effect):源体间电势差增大也会抬升 $V_t$

- 漏致势垒降低(drain-induced barrier lowering):增大漏压会降低 $V_t$

- 短沟道效应(short channel effects):沟道变长将抬升 $V_t$

泄露(leakage)现象:在关断的 MOS 中仍有电流流动

- 亚阈值导通(subthreshold conduction):$V_{gs}<V_t$ 时,电流以指数形式下降而不是突变为 0,因此关断后会在极短时间内有电流导通

- 结泄露(junction leakage):源漏极与体(衬底或井)间的反向偏置 PN 结有微小电流

- 门泄露(gate leakage):栅氧极薄时将发生电子隧穿(electron tunneling)有微小栅极电流

温度影响:高温 => 低移动力,低 $V_t$,导通时低 $I_{ds}$,关断时高泄露;MOS 特性退化。

关于 pMOS

见上图右侧的曲线,把 $V_{ds}$ 换成 $V_{sd}$,$I_{ds}$ 换成 $I_{sd}$,整个曲线镜像到第一象限,就与 nMOS 同样是开口向下的二次曲线了。但很明显开口比 nMOS 要小,这是因为空穴移动力 $\mu_{p}$ 约是电子移动力 $\mu_{n}$ 的一半。

这也呼应了之前提到的,pMOS 与 nMOS 提供同样的电流,宽度须是后者的两倍。