栅-沟道电容

简称为栅电容(gate capacitance)。它是必要的,产生器件工作所需的沟道电荷。

- 上极板:栅极

- 下极板:与源极连接的沟道(饱和时沟道将在近漏处消失,因此不计入漏极)

- 绝缘介质:栅氧

见上一节式 $(3)$,栅电容有:

$$

C_g=C_{ox}WL

$$

大多数晶体管采用工艺允许的最小可制造沟道长度,可将 $L$ 视为某一工艺下的常数。因有:

$$

C_g=C_{permicron}W \quad \text{where} \quad C_{permicron}=C_{ox}L=\frac{\varepsilon_{ox}}{t_{ox}}L

$$

若更先进的制造工艺能使沟道长度 $L$ 与栅氧厚度 $t_{ox}$ 按相同倍数缩小,$C_{pemicron}$ 保持不变。该量的物理含义是 capacitance per micron,即每 1 微米的晶体管宽度所增加的栅电容。

- $C_{permicron}$ 常取 $2 \ fF/\mu m$

极-体电容

极-体电容又被称为

- 寄生电容(parasitic capacitance):说明此电容 undesirable

- 扩散电容(diffusion capacitance):与源漏扩散区有关

源漏扩散区与体区形成的 PN 结间会形成一个不含自由载流子的耗尽区,以充绝缘介质。这些结电容的大小与扩散区的面积,周长,深度,掺杂水平与端电压有关。

- (扩散区)底部结电容

- (扩散区)侧壁结电容

带接触孔的扩散电容 $C_{sb}, C_{db}$ 与甚至与栅电容 $C_g$ 量级相当。无接触孔者则约为 $C_g/2$。

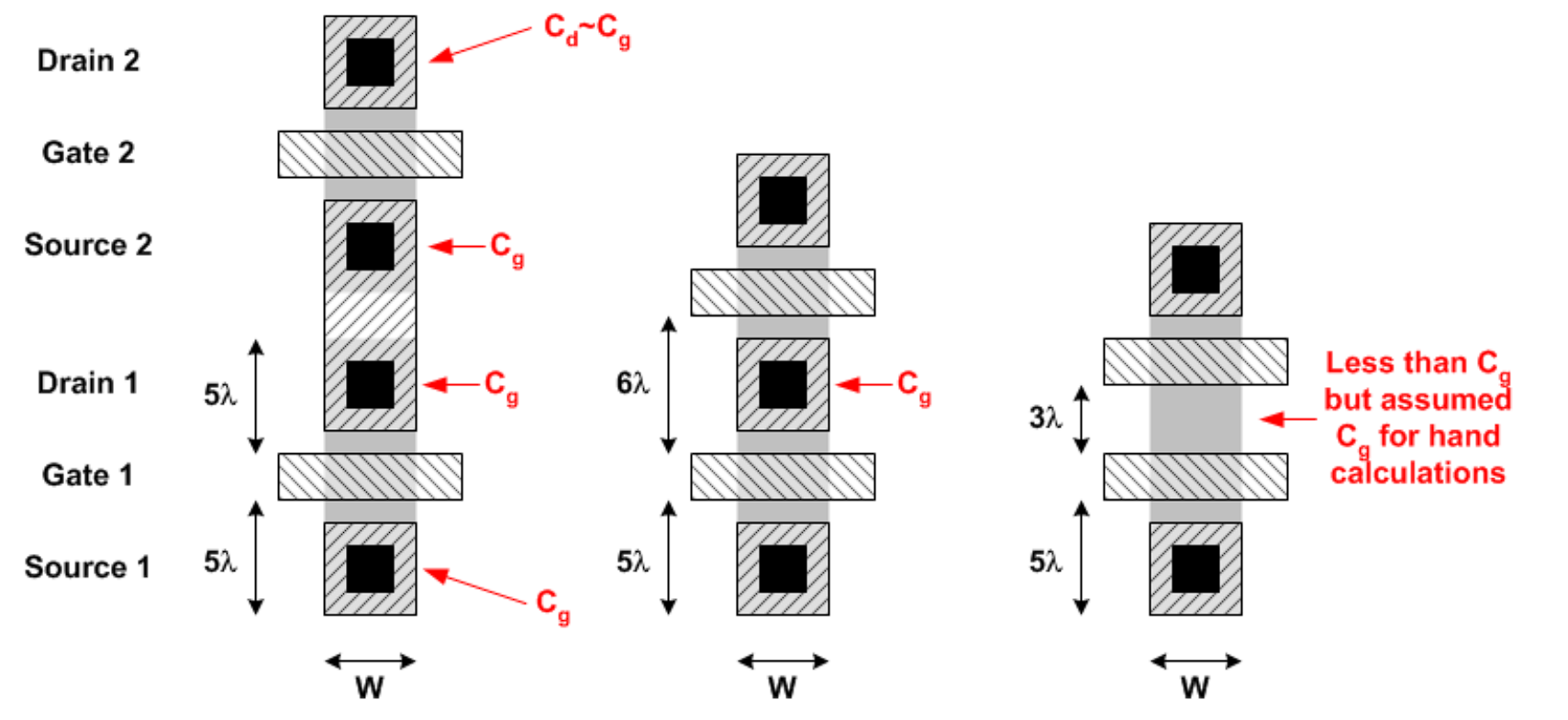

常见的扩散区几何形态有三种,以两串联晶体管为例:

从左至右依次为独立扩散区(isolated diffusion),共享扩散区(shared diffusion)与合并扩散区(merged diffusion),其扩散电容越来越小。