大一时候写的 1310 笔记发挥了一点用处,可以参考 此处。

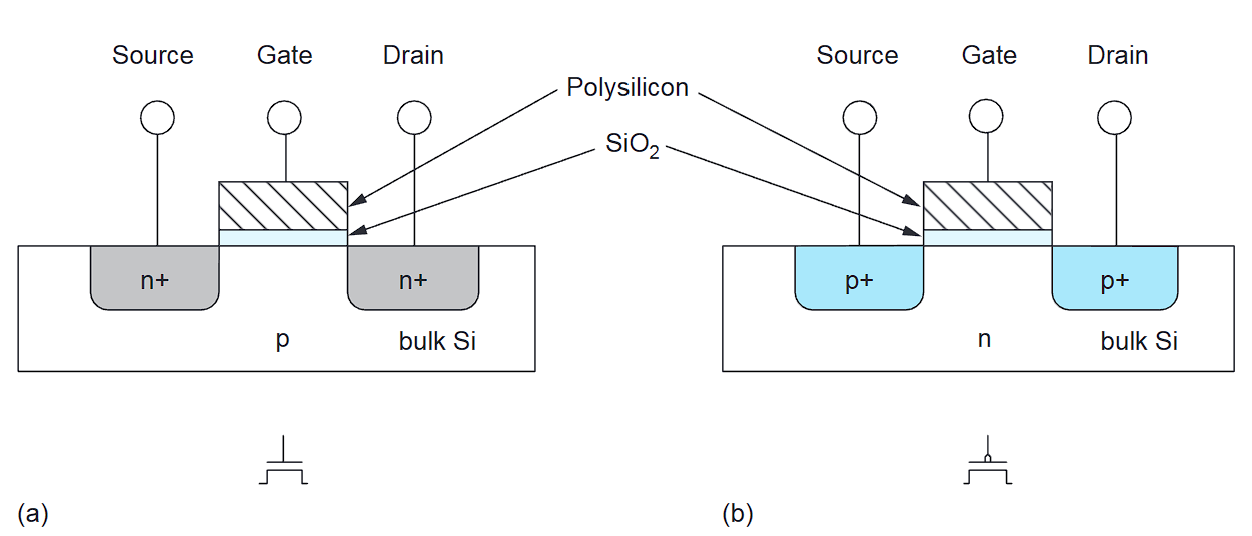

MOS 晶体管

硅(Silicon),IV 族,导电性差

在硅晶格中引入掺杂剂(dopants)增加导电性,称为半导体(semiconductor)

- 砷(arsenic, As),V 族,砷原子的第五个价电子束缚弱 => n 型半导体,载流子(carrier)是带负电的自由电子

- 硼(boron,B),III 族,空穴 => p 型半导体,载流子是带正电的空穴

- p 型半导体侧为

阳极(anode) ,n 型半导体侧为阴极(cathode) - 外电场 p -> n 为

正向偏置(forward biased) ,n -> p 为负向偏置(reverse biased)

金属氧化物半导体(Metal-Oxide-Semiconductor, MOS)或 金属氧化物半导体场效应晶体管(MOS Field Effect Transistors, MOSFETs)

- 栅极 Gate

- 衬底 Substrate, Body, Bulk

- 源极 Source,漏极 Drain,载流子通过沟道(channel)由源极流向漏极

栅极电压 $V_G$,源极电压 $V_S$,阈值电压 $V_T$

- nMOS:栅极电压 $V_{DD}$(逻辑 1, 或 POWER),$V_{GS}=V_G-V_S\geq V_T$ 时导通 ON

- pMOS:栅极电压 $V_{SS}$(逻辑 0, 或 GROUND),$|V_{GS}|=|V_G-V_S|\geq V_T$ 时导通 ON

- overdrive 电压:$V_{ov}=V_{GS}-V_T$

静态 CMOS 逻辑门

nMOS + pMOS = wavy CMOS(互补金氧半,Complementary MOS)。互补的晶体管放在衬底中的井中(n 衬底 p 井,反之)。

经典的静态 CMOS 逻辑门包含两个网络:

- nMOS

下拉网络(pull-down network, PDN) ,连接 $V_{SS}$ 和输出,负责导通时传递强 0(下拉) - pMOS

上拉网络(pull-up network, PUN) ,连接 $V_{DD}$ 和输出,负责导通时传递强 1(上拉)- PUN ON,PDN OFF:上拉至 1

- PUN OFF,PDN ON:下拉至 0

- PUN OFF,PDN OFF:高阻(high-impedance)或浮接(floating)态,记为 Z

- PUN ON,PDN ON:短路(crowbarred)或竞(contention)态,记为 X

反相器(Inverter),i.e.,非门(NOT Gate):单 nMOS PDN 和单 pMOS PUN

与非门(NAND Gate),$k$ 个串联的 nMOS PDN 和 $k$ 个并联的 pMOS PUN

或非门(NOR Gate),$k$ 个串联的 pMOS PUN 和 $k$ 个并联的 nMOS PDN

复合门(Compound Gate),给定表达式 $Y$ 画出电路图(schematic)

- 画 PDN,由于需要把表达式下拉至 0,又 nMOS 栅极输入 1 导通,把表达式 $Y$ 取反后组装

- 画 PUN,由于需要把表达式上拉至 1,又 pMOS 栅极输入 0 导通,把表达式中所有的变量取反后组装(或使用

conduction complements 原则,把 PDN 中串联改并联,并联改串联即可)

性质一:静态 CMOS 逻辑门是

点一下睡袋(呸) 指一个逻辑级在稳态时能把输出节点强驱动(strongly driven)到接近电源轨的全摆幅电平(0 或 $V_{DD}$),并通过带增益把可能劣化的输入电平拉回到标准逻辑电平,使电平劣化不会在级联中继续累积。静态 CMOS 逻辑中 nMOS 只负责下拉至强 0,pMOS 只负责上拉至强 1,且二者互斥,因此输出电平一定是全摆幅的。

性质二:静态 CMOS 逻辑门是

指该逻辑级实现的布尔关系在输出端带有一个逻辑取反,即输出等于某个函数的补 $y=\overline{f(x)}$;比如非门 $y=\overline A$,与非门 $y=\overline{A\cdot B}$, 或非门 $y=\overline{A+B}$。

这也是为什么最基础的物理逻辑门是 NOT,NAND,NOR 而不是 OR,AND;这天然的由 MOS 的物理特性与 CMOS 的设计原则决定:输入为 1 会使基于 nMOS 的 PDN 导通,从而使输出为 0;反之 PUN 同理。

可以直接拼非反相的 $y=f(x)$ 吗?当然可以,但需要多加一级反相器 $y=\overline{\overline{f(x)}}$,这意味着更高的延迟,功耗和面积。

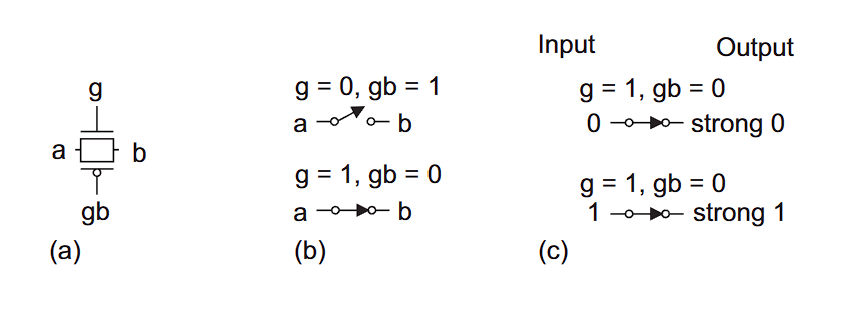

传输门

传输门(Transmission Gate),解决了通道晶体管阈值损失的问题。

需要同时提供控制输入(control input)信号 $g$ 与其互补信号 $gb$ 的逻辑被称为

传输门的输出电压来自上一级节点,而非 $V_{DD}$ 或 GND,没有驱动能力,因此是 non-restoring 的。它的理想行为近似 $V_{in}\approx V_{out}$,为同向传输,并非反相。

三态逻辑

三态逻辑(tristate)指的是三种输出驱动状态:低电平 $0$, 高电平 $1$ 与高阻态 $Z$。

三态缓冲器(tristate buffer):逻辑功能与传输门相同(真值表一致),但它的输出电压来自 VDD 与 GND,因此是 restoring 的,能够保证输出一定是三态中的其中一个。

| $EN/\overline{EN}$ | $A$ | $Y$ |

|---|---|---|

| 0/1 | 0 | Z |

| 0/1 | 1 | Z |

| 1/0 | 0 | 0 |

| 1/0 | 1 | 1 |

三态反相器(tristate inverter):EN 为 0 时两个晶体管均关断,输出为 $Z$,EN 为 1 时表现与反相器一致。restoring。

三态总线(tristate bus):现已被多路复用器替代。

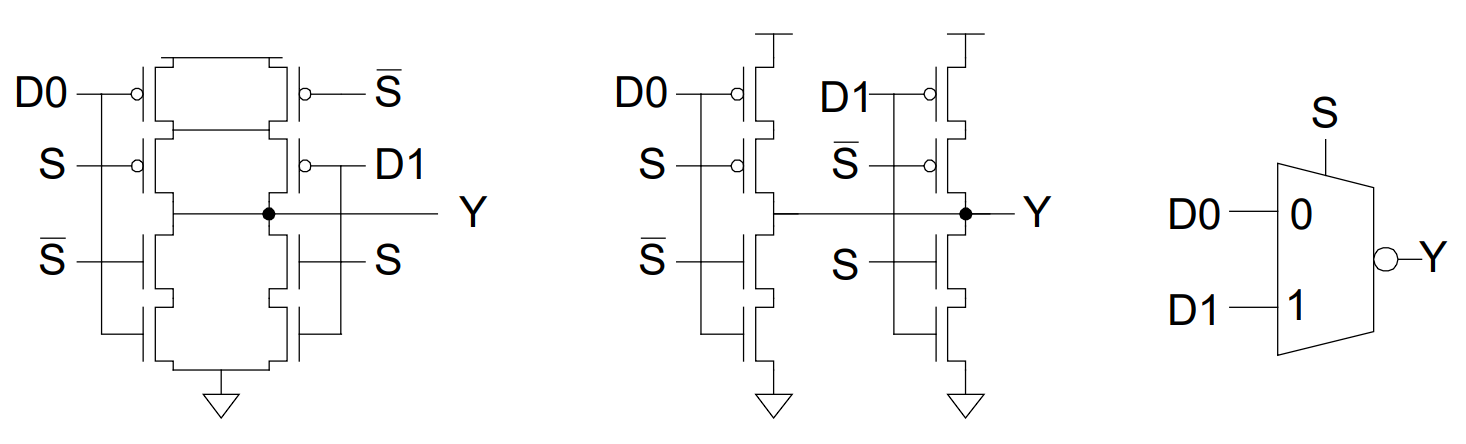

多路复用器

多路复用器(multiplexer, MUX)是 CMOS 存储单元(memory elements)与数据处理结构中的关键组件。它通过选择信号(select signal)$S/\overline{S}$ 在多个输入中选择一个作为输出。

譬如 2:1 MUX,选择信号为 0 时选择输入 $D0$,选择信号为 1 时选择输入 $D1$,逻辑函数为:

$$

Y=\overline{S}\cdot D0+S\cdot D1

$$

2:1 MUX 的几个实现方式

- 传输门 MUX:两个传输门连接在一起,选择信号 $S$ 与其互补信号 $\overline{S}$ 在任意时刻只会使其中一个传输门导通。这样组成的 MUX 是 non-restoring 的,仅需要四个晶体管。

- 反相 2:1 MUX($Y=(\overline{\overline{S}\cdot D0+S\cdot D1})$):复合 AOI22 电路或两个三态反相器并联。连接一个反相器负负得正成 2:1 MUX。这样组成的 MUX 是 restoring 的。

4:1 MUX:使用两个选择信号 $S0$, $S1$ 从四个输入中选择一个作为输出。两层 2:1 MUX 或四个三态反相器并联。

时序逻辑

组合逻辑(combinatorial logic)的输出只取决于当前输入。时序逻辑(sequential logic)有 memory,其输出由当前输入与 memory 共同决定。时序逻辑元件接收时钟信号(clock)CLK 与输入 $D$,产生输出 $Q$。

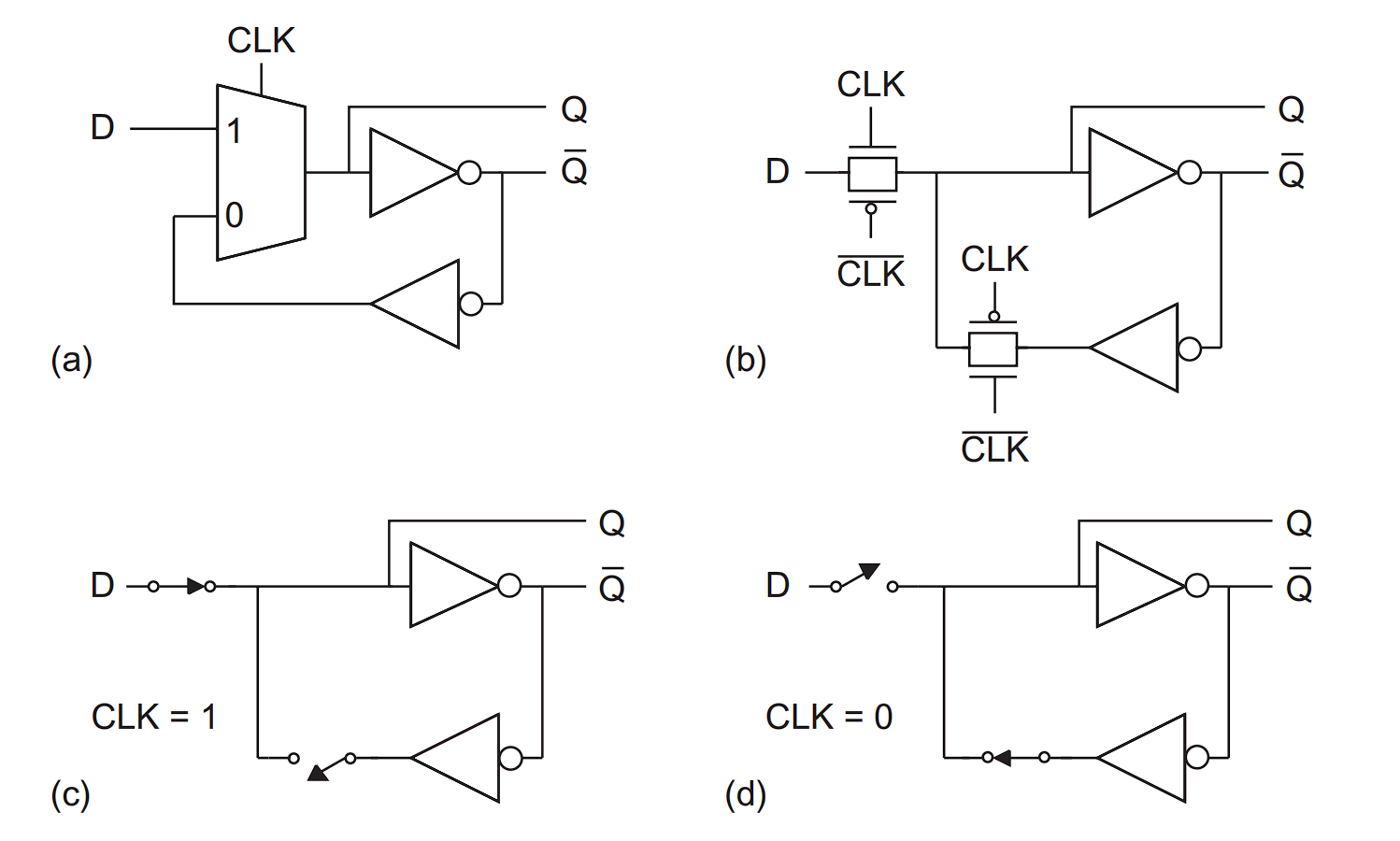

D 型锁存器

锁存器(latch)直译为门闩。

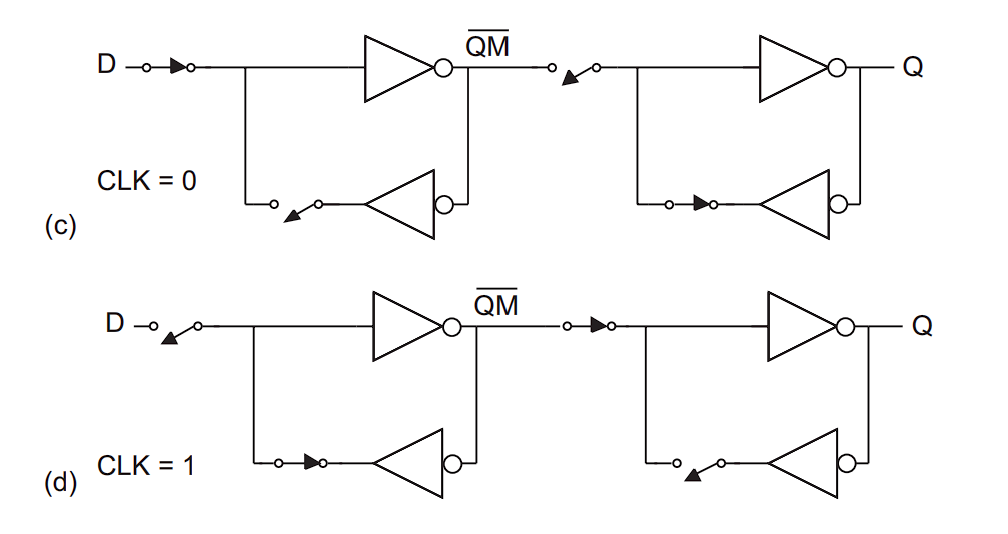

D 型锁存器的行为 (c) (d):

- CLK 为 1:锁存器透明(transparent),当前输入 $D$ 传递至输出 $Q$,同时产生互补输出 $\overline{Q}$

- CLK 为 0:锁存器不透明(opaque),反馈回路将当前输出 $Q$ 锁起来,保持当前状态

D 型锁存器也被称为电平敏感锁存器(level-sensitive latch),因为输出状态取决于 CLK 的电平高低。

D 型触发器

触发器(flip-flop)直译为翻转,跳动。

D 型触发器由一对串联的电平敏感锁存器构成,前者为主锁存器(master latch),是负电平敏感的;后者为从锁存器(slave latch),是正电平敏感的。

D 型触发器的行为 (c) (d):

- CLK 由 0 跳变为 1:主锁存器结束对输入 $D$ 采样(sampling),将这一时刻的采样值传递至从锁存器的输出 $Q$,刷新记忆

- CLK 由 1 跳变为 0:主锁存器开始对输入 $D$ 采样,从锁存器锁住,保持先前的记忆

D 型触发器也被称为边沿触发器(edge-triggered flip-flop),因为它只在 CLK 从 0 到 1 跳变的这一「上升沿」瞬间采样输入 $D$ 并更新到输出 $Q$;其余时间,如 CLK 稳定为 0/1 或从 1 到 0 跳变,其输出均维持不变。

时钟偏移

时钟信号到达电路各个部分所用的时间是有差异的,这被称为时钟偏移(clock skew)。

考虑两个串联的触发器 FF1 与 FF2,$D_1 \to$ FF1 $\to Q1 \to$ FF2 $\to Q2$。某时 CLK 从 0 跳变至 1,这一瞬间理想的行为是:

- FF1 采样并存入 $D1’$

- FF2 采样并存入 $Q1$

但由于时钟偏移的存在,FF2 CLK 的跳变迟于 FF1 CLK 的跳变,那么 FF2 采样的可能是已经被 FF1 更新过后的 $D1’$。这是一种被称为保持时间违例(hold-time failure) 的竞态(race condition)现象。

解决方法:

- 两相不重叠时钟(non-overlapping clocks):使用多个时钟相位,在触发器中,主锁存器被 $\phi_2$ 控制,从锁存器被 $\phi_1$ 控制;令 $\phi_1$ 与 $\phi_0$ 不得同时跳变,不重叠区域为至少一个时钟偏移的时间,从而阻断采样到储存的通路【见 Lec 2 p.37】只能用于规模较小的项目

- 时钟树综合(clock tree synthesis, CTS)与静态时序分析(static timing analysis, STA)