电路的直流传输特性(DC transfer characteristics)描述了其输出电压 $V_{out}$ 与输入电压 $V_{in}$ 间的稳态对应关系。

静态 CMOS 反相器直流特性

考虑一个 CMOS 反相器,令其 pMOS 晶体管宽度是 nMOS 的 2 - 3 倍以使 $\beta_{n}=\beta_{p}$,并假设两者阈值电压(绝对值)一致 $V_{tp}=-V_{tn}$。

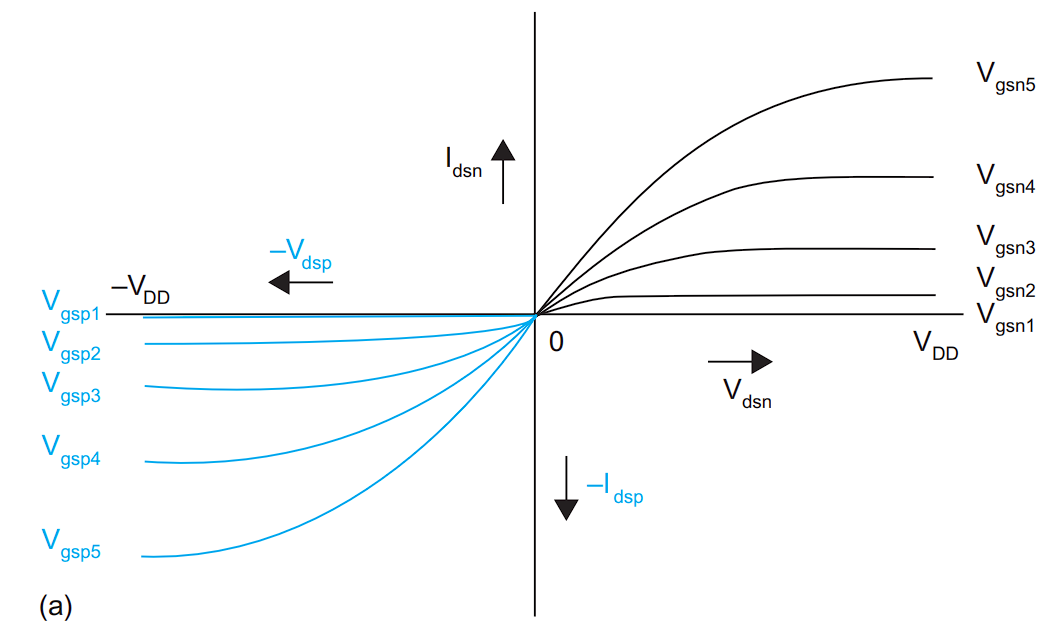

对于 nMOS,$V_{in}=V_{gsn}, V_{out}=V_{dsn}$,电流由漏流向源所以 $I_{dsn}>0$,阈值电压 $V_{tn}>0$。

pMOS 则因为源极 s 连接 VDD,所以有 $V_{in}=V_{gsp}+V_{DD}, V_{out}=V_{dsp}+V_{DD}$,电流由源流向漏所以 $I_{dsp}<0$,阈值电压 $V_{tp}<0$。

分别对 nMOS 与 pMOS 作 IV 特性图,栅压绝对值对应:$V_{gsp:x}=-V_{gsn:x}$

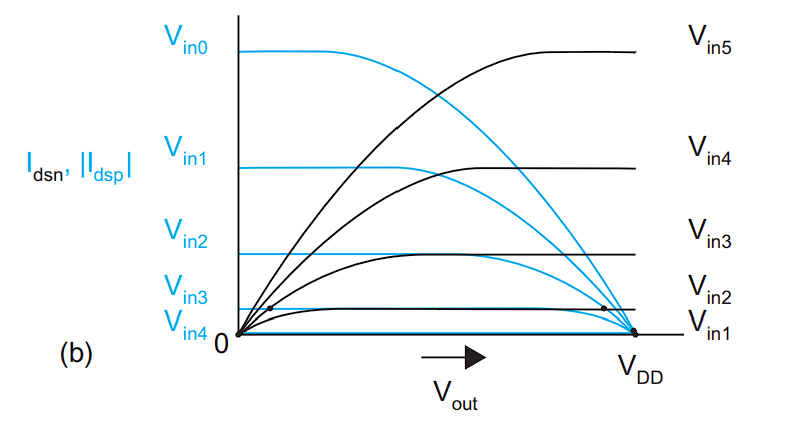

因之前的假设,nMOS 和 pMOS 的器件参数一致,所以曲线完全对称。接下来,取 $I_{dsp}$ 的绝对值(按 $x$ 轴翻转),将 $x$ 轴改成 $V_{out}$(nMOS 曲线不变,pMOS 曲线右移 $V_{DD}$),再把栅压 tag 改成 $V_{in}$(nMOS tag 不变,pMOS tag 增加 $V_{DD}$),就得到:

注意这里 $V_{in0}$ 对应的是 GND,$V_{in5}$ 对应的是 VDD。根据基尔霍夫电流定律 KCL,电路最终必须稳定在 $I_{dsn}=|I_{dsp}|$ 的点。连接相同 $V_{in}$ 下的交点,画 $V_{in}$-$V_{out}$ 图:

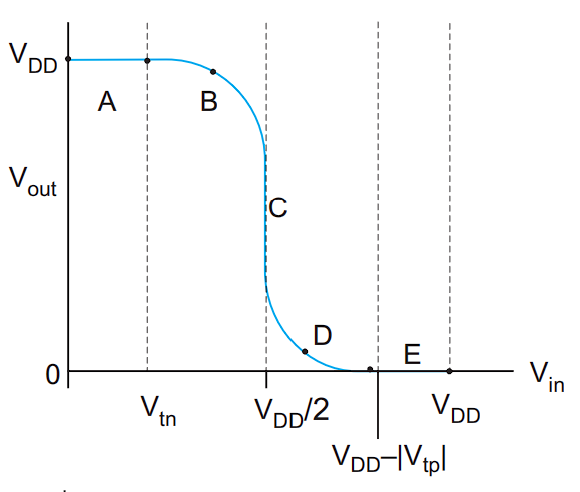

这就是反向器的直流特性图了。从中可以很明显见出 nMOS 与 pMOS 所在的不同区域:

- A 区:nMOS 关断,pMOS 线性

- B 区:nMOS 饱和,pMOS 线性

- C 区:nMOS 饱和,pMOS 饱和(理想晶体管此时有 $V_{in}=V_{out}=V_{DD}/2$,斜率无限大)

- D 区:nMOS 线性,pMOS 饱和

- E 区:nMOS 线性,pMOS 关断

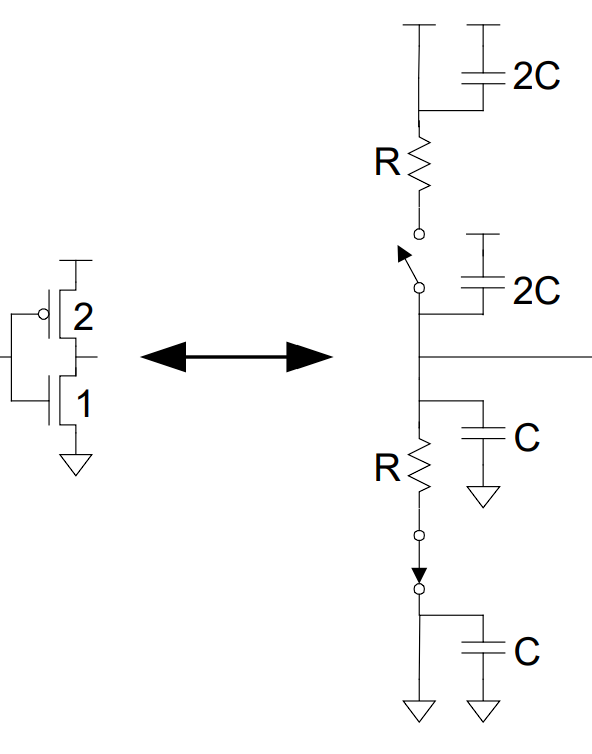

配合反相器的 RC 模型食用更佳。$V_{in}$ 决定开关的「打开程度」,$V_{out}$ 是稳态的输出电压。

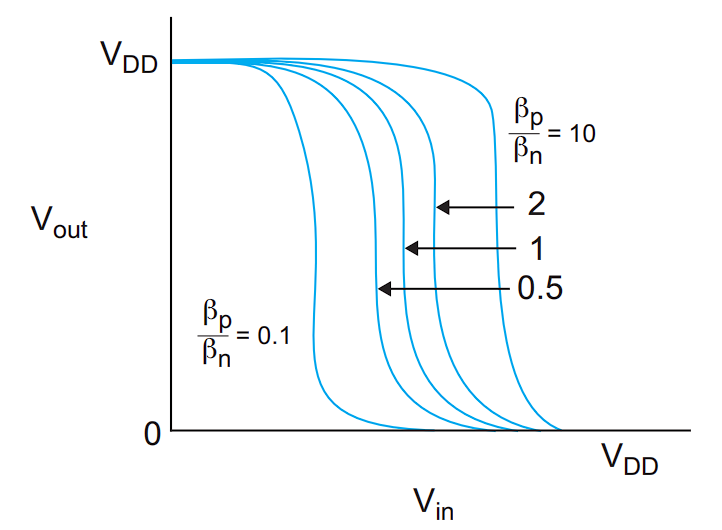

β 比值效应

$\beta=\mu C_{ox}\frac{W}{L}$ 描述的是晶体管驱动能力的强弱。$\beta$ 越大,晶体管在相同栅压条件下能提供的电流就越大。如前所述,当 $\beta_n=\beta_p$ 时,反相器的阈值电压 $V_{inv}$ 恰好是 $V_{DD}/2$。

又称开关阈值(switching threshold),指的是 $V_{in}=V_{out}$ 时对应的输入电压。此时反相器的输出正好处在翻转临界状态。

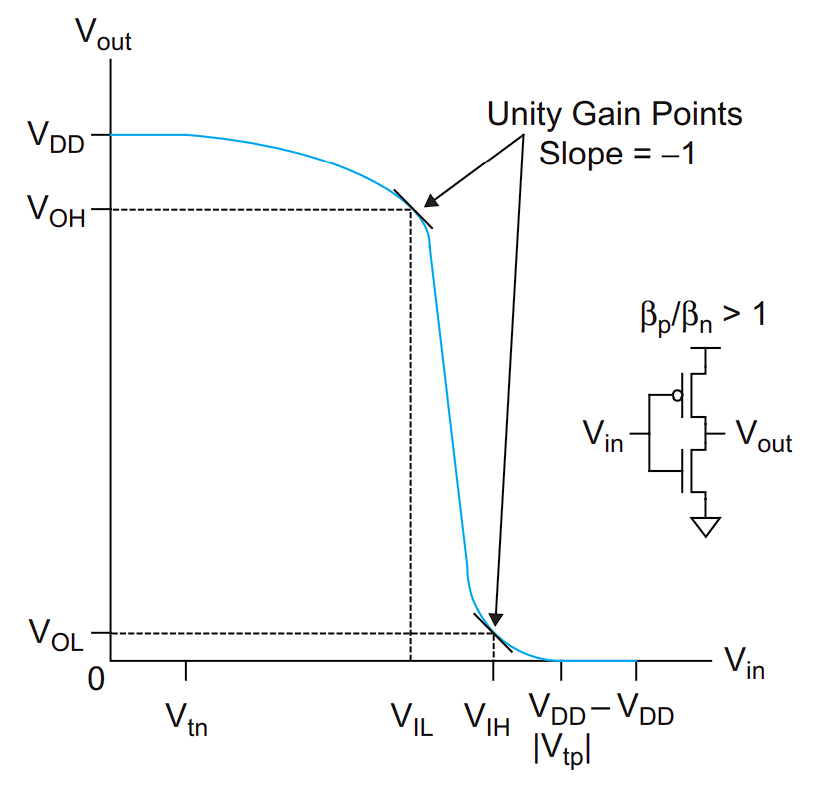

令 $r=\beta_p/\beta_n$

- 无偏(unskewed)反相器:$r=1$,$V_{inv}=V_{DD}/2$

- 高偏(HI-skewed)反相器:$r>1$,pMOS 驱动强于 nMOS 驱动,$V_{inv}>V_{DD}/2$

- 低偏(LO-skewed)反相器:$r<1$,nMOS 驱动强于 pMOS 驱动,$V_{inv}<V_{DD}/2$

分析静态 CMOS 门时,常计算 PUN 和 PDN 的等效驱动能力,再把整个门近似成一个具有某个等效 $\beta_p$ 和 $\beta_n$ 的反相器,这样就能用反相器的分析方法去估计它的阈值电压和延迟。

- 串联晶体管:等效为更长 $L$ 的单个晶体管

- 并联晶体管:等效为更宽 $W$ 的单个晶体管

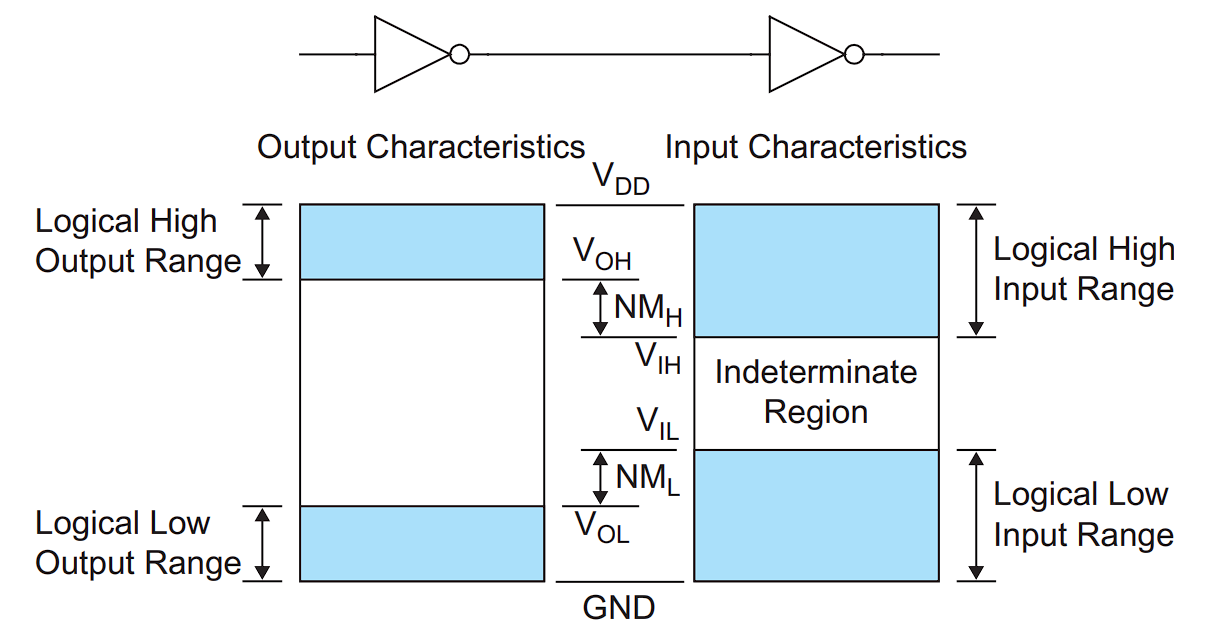

噪声裕度

噪声裕度(noise margin)的划分决定某个逻辑门输入端允许叠加多大的噪声电压而不会使得输出被破坏。有低电平噪声裕度 $NM_L$ 与 高电平噪声裕度 $NM_H$:

- $NM_L$:接收门识别的最大低电平输入 $V_{IL}$ 与驱动门产生的最大低电平输出 $V_{OL}$ 之差

- $NM_H$:驱动门产生的最小高电平输出 $V_{OH}$ 与接收门识别的最小高电平输入 $V_{IH}$ 之差

给定一个 CMOS 门的直流特性图,一个保守的做法是在单位增益点(unity gain point)划定 $V_{OH}$ 与 $V_{OL}$ 以最大化最坏情况下的噪声裕度。

单位增益点是斜率 $k=-1$ 时所对应的点,当$|k|<1$ 时,曲线比较平缓,输入中的噪声不会被明显放大;当 $|k|>1$ 时,曲线开始变得陡峭,输入的微小扰动会引起输出很大变化,此刻就不适合将其视为稳定的逻辑 0 或逻辑 1。