Bubble Pushing

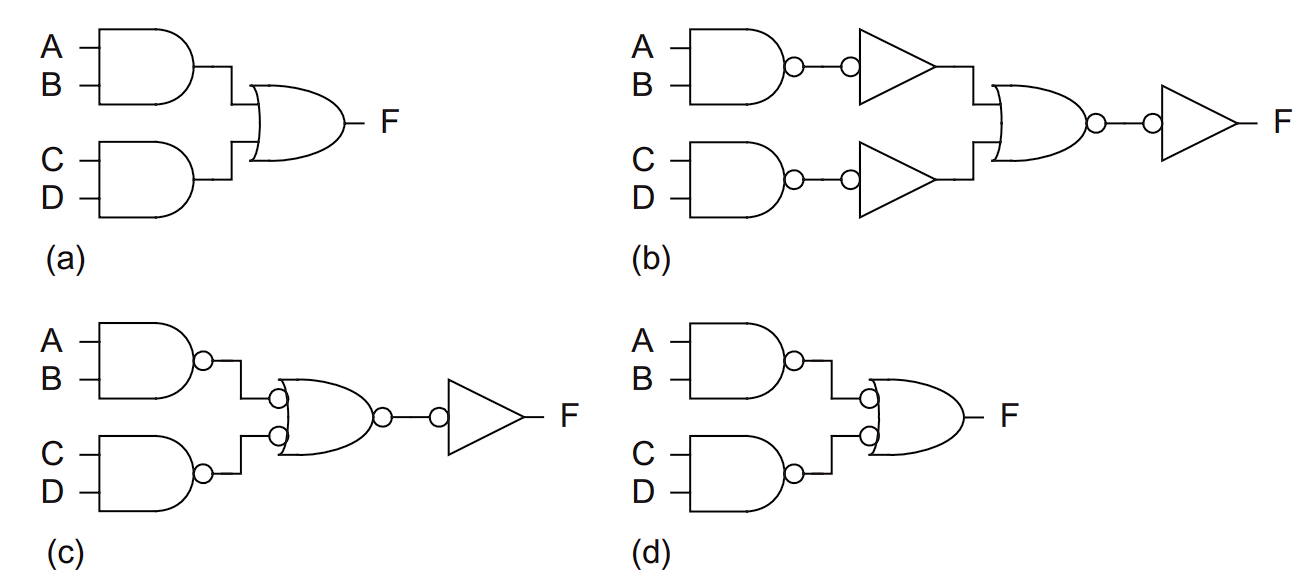

CMOS 逻辑门是内生反相的,AND 和 OR 功能必须由 NAND 或 NOR 门来实现。利用 De Morgan 定律实现这种转换,在电路图上的反映被称为气泡推拉(bubble pushing)。

一次转换:气泡从输入/输出,门从 AND/OR;$\overline{A\cdot B}=\overline{A}+\overline{B}, \overline{A+B}=\overline{A}\cdot\overline{B}$。

复合门

上例中,$F=\overline{AB+CD}$ 采取的是 NAND solution。若最大输入电容为 16,负载电容为 160,有:

- 寄生电容 $P=2+2=4$

- 逻辑努力 $G=(4/3)\cdot(4/3)=16/9$

- 电气努力 $H=160/16=10$

- $F=GH=160/9$

- 最佳级努力 $\hat{f}=\sqrt[N]{F}=4.2$

- 延迟 $P=N\hat{f}+P=12.4\tau$

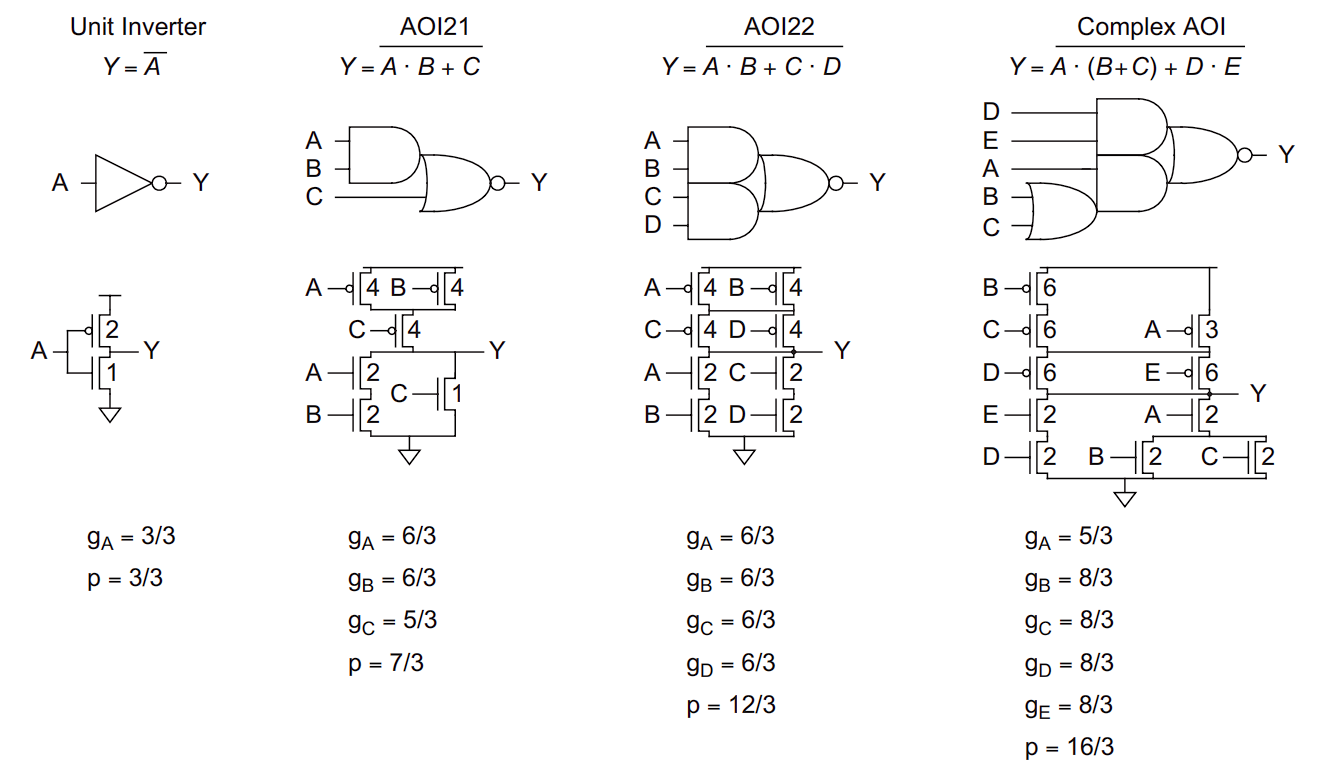

AND-OR-INVERT-22(AOI22)采取的则是复合设计 compound solution:

- 寄生电容 $P=4+1=5$

- 逻辑努力 $G=(6/3)\cdot(1)=2$($P,G$ 均可见下图分析)

- $F=GH=20$

- 最佳级努力 $\hat{f}=\sqrt[N]{F}=4.5$

- 延迟 $P=N\hat{f}+P=14\tau$

复合门将多个基本逻辑门打包成一个功能单元,减少电路级数。

输入顺序

Input Ordering

定义

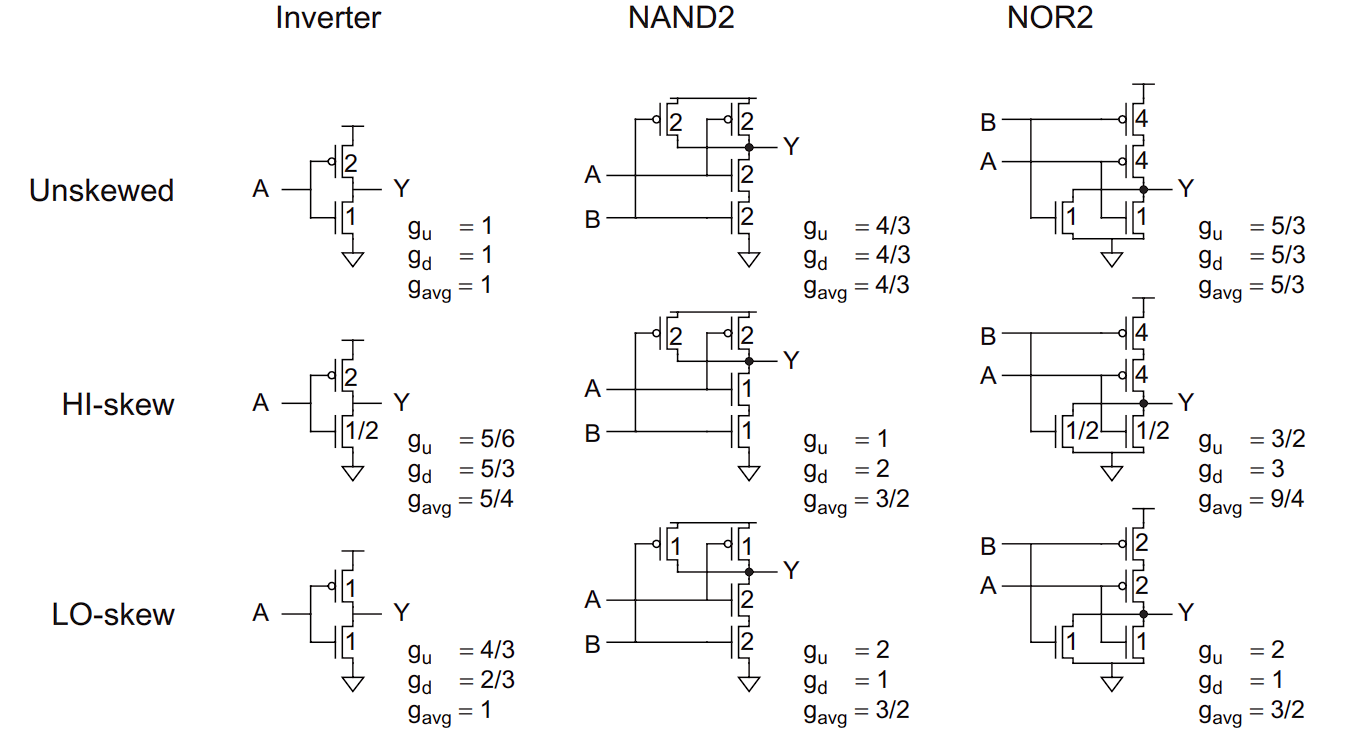

再谈偏斜门

高偏(HI-skewed)门 pMOS 端电阻更小,偏好输出上升沿(rising edge);低偏(LO-skewed)门 nMOS 端电阻更小,偏好输出下降沿(falling edge)。

偏斜门在某一特定跳变方向(a particular transition)上的逻辑努力,是指该门的输入电容与一个无偏反相器的输入电容之比 —— 其中该无偏反相器在相同跳变方向上能提供相同的输出电流。

根据该定义,求某偏斜门的逻辑努力:

- 上升沿 $g_u$:取一个与待求门 pMOS 端等效电阻相同的无偏反相器,计算输入电容之比

- 下降沿 $g_d$:取一个与待求门 nMOS 端等效电阻相同的无偏反相器,计算输入电容之比

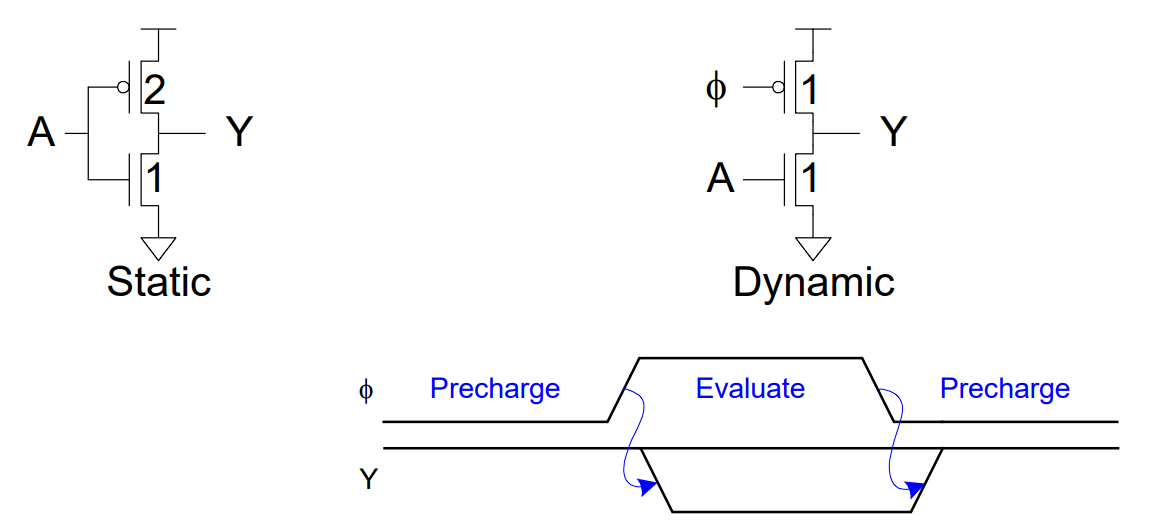

动态逻辑与多米诺门

时钟信号 $\phi$ 初始为 0,动态电路预充电将输出电平拉高;$\phi$ 变为 1,动态电路进入求值阶段,对输入 $A$ 进行求值。若输入为真,输出电平被拉低;反之保持高。

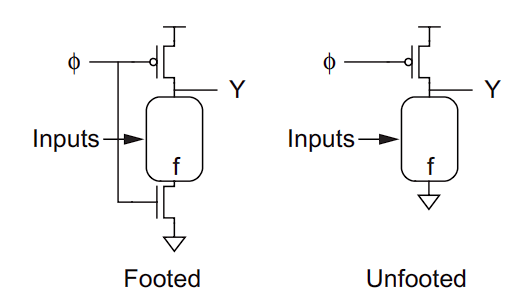

问题一:预充电阶段,时钟信号与输入信号双高导致争用(contention)。解决方法是引入 foot:一个串联在 nMOS 下拉网络底部的时钟控制晶体管,在预充电阶段阻断输入信号与地线。

- 输入 $X$ 从 $0\to 0$:输出 $Y$ 从 $1\to 1$

- 输入 $X$ 从 $0\to 1$:输出 $Y$ 从 $1\to 0$

- 输入 $X$ 从 $1\to 1$:输出 $Y$ 从 $0\to 0$

- 输入 $X$ 从 $1\to 0$:求值阶段时钟信号阻断了电源轨,输出 $Y$ 无法从 $0$ 拉到 $1$

解决方法是

- 一系列级联的多米诺门并行 parallel 预充电(受同一时钟信号控制),相继 sequential 求值(前门的输出是后门的输入);是不是很像多米诺骨牌纷纷倒下?

- 求值阶段比预充电阶段更 critical(是延迟的 bottleneck)

- 静态反相器通常是 HI-skewed 的,能够将动态电路单调不增的输出拉高成单调不降

解决方法:

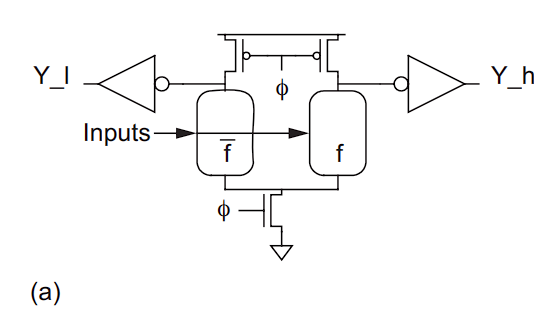

输出信号 $Y$ 同时被 $Y_l$ 与 $Y_h$ 表示。预充电阶段两者均为 0,$Y_h=1$ 表示 $Y=1$,$Y_l=1$ 表示 $Y=0$。正常工作时两者不应同时为 1。这样,即使对于 NAND, NOR 与 XOR 这样的反相函数,也能做到求值阶段每根线上均单调不降。

| $Y_h$ | $Y_l$ | 含义 |

|---|---|---|

| 0 | 0 | 预充电 |

| 0 | 1 | 求值 ‘0’ |

| 1 | 0 | 求值 ‘1’ |

| 1 | 1 | 无效 |

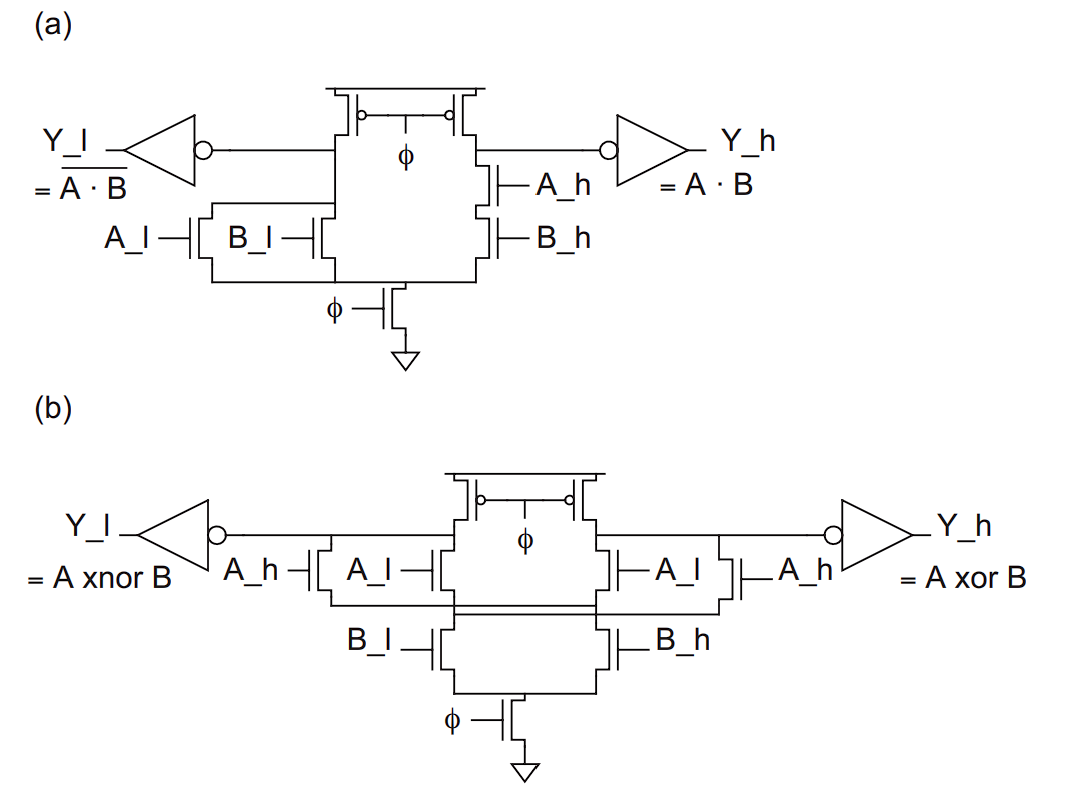

其实就是把 conduction complements 引入了 nMOS 网络。对于函数 $F(A,B)$,$Y_h$ 端用 $A_h, B_h$ 拼出 $F$,$Y_l$ 端用 $A_l, B_l$ 拼出 $\overline{F}$。

XOR 在 $Y_l, Y_h$ 路径上共用了晶体管,显得有点难以理解。

- $Y_h=B_hA_l+B_lA_h=B\overline{A}+\overline{B}A=A\text{ XOR } B$

- $Y_l=B_lA_l+B_hA_h=\overline{B}\cdot\overline{A}+BA=A\text{ XNOR }B$

解决方法是引入保持器(keeper),一个足够弱的 pMOS 晶体管。当 nMOS 导通时不会强到影响求值,nMOS 关断时足够「吊着」高电平。

问题五:电荷共享(charge sharing)。求值阶段,内部节点可能分走高电平。若内部扩散电容 $C_x$ 过大,输出电平甚至可能被拉低到 0。$$

V_{\text{final}}=\frac{C_Y}{C_x+C_Y}V_{DD}

$$

解决方法:引入

多米诺门总结:

- 只有 nMOS 求值网络 critical,比静态 CMOS 快 1.3-2 倍,适于做高速电路

- 噪声敏感,高能耗

- 90 年代流行(以复杂设计换速度),现已被静态 CMOS 取代(能耗成为第一约束)

传输晶体管逻辑

在传输晶体管电路(pass transistor circuits)中,输入不单止加在栅极端,也会加在源/漏扩散端。一个典型例子见 CMOS 逻辑一节中的传输门(transmission gate)。

- CMOS 与传输门混合使用:MUX,latch

- 互补传输晶体管逻辑(CPL):全加器

- LEAn integration with Pass transistors(LEAP)

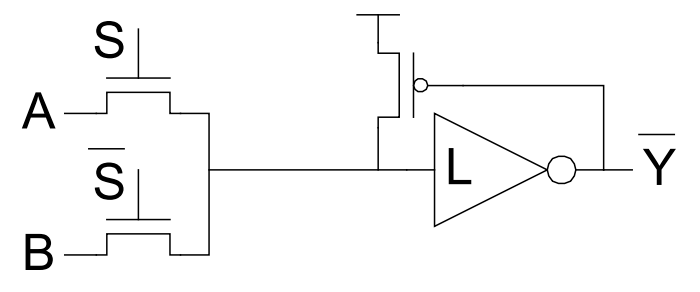

LEAP 属于单端逻辑电路,只使用速度较快的 nMOS 晶体管,不需要 pMOS 互补网络。

- 左侧:仅由 nMOS 构成,单端逻辑

- nMOS 传 0 强 1 弱。若传 1,只能升到约 $V_{DD}-V_t$。

restoring 逻辑 :接一个 LO-skew 反相器,翻转阈值 $V_{inv}$ 较低,从而能够把弱 1 翻转过来。之后的弱 pMOS 反馈回路激活,把弱 1 拉高成满摆幅强 1(fully high)。

传输晶体管逻辑易出现电平退化,因此通常需要接 restoring 门。