直流分析关注稳态:当输入 $V_{in}$ 为常数时,输出 $V_{out}$ 稳定后的数值。瞬态分析(transient analysis)则关注当输入 $V_{in}$ 变化时,输出 $V_{out}$ 的变化。

瞬态分析常研究阶跃输入(step/ramp input)的响应。即输入由 0 突变到 VDD 或从 VDD 突变到 0。相应的,输出的变化即是阶跃响应(step response)。

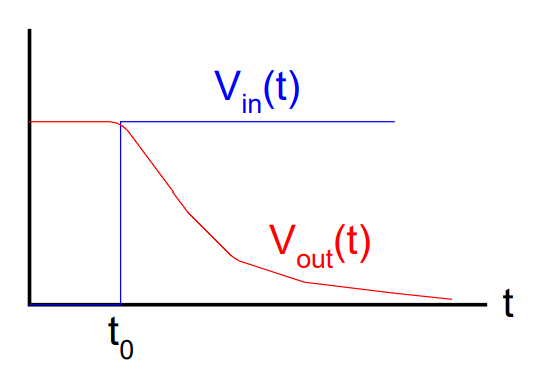

反相器阶跃响应

考虑一个有负载电容的理想反相器。在时刻 $t_0$ 施加一个上升的阶跃电压,有:

$$

V_{in}(t)=u(t-t_0)V_{DD}

$$

在 $t_0$ 之前,$V_{out}=V_{DD}$,研究 $V_{out}(t\geq t_0)$。考虑电容充电放电的微分方程:若电容 $C$ 以电流 $I$ 充电,电容两端的电压变化遵循:

$$

I=C\frac{dV}{dt}

$$

那么对于施加上升阶跃输入的反相器而言,nMOS 开启,$I_{dsn}$ 开始流动为负载电容放电,有:

$$

\frac{dV_{out}(t)}{dt}=-\frac{I_{dsn}(t)}{C_{load}}

$$

nMOS 的输出极为漏极,源极接地,所以输出电压为漏源电压 $V_{out}=V_{ds}$。代入 nMOS 的一阶晶体管模型(见「IV 特性」一节),有:

$$

\begin{equation}

\frac{dV_{out}(t)}{dt} =

-\frac{I_{dsn}(t)}{C_{load}} =

-\frac{\beta}{C_{load}}

\begin{cases}

0, & t \leq t_0 \\

\dfrac{(V_{DD}-V_t)^{2}}{2},

& V_{out} > V_{DD}-V_t \\

\left(V_{DD}-V_t-\frac{V_{out}(t)}{2}\right)V_{out}(t),

& V_{out} < V_{DD}-V_t

\end{cases}

\end{equation}

$$

作出理想反相器的上升阶跃响应图:

nMOS 导通后,首先进入饱和区,电流固定,输出电压线性下降,直到达到 $V_{DD}-V_t$,此后进入线性区,输出电压非线性的下降(但电流是近似线性下降的!)。$\beta_n=\beta_p$ 时,下降阶跃响应是对称的。

反相器斜坡响应

实际电路中的输入信号来自另一个逻辑门,因此其上升或下降时间并不为 0(非阶跃)。同样考虑一个上升的输入信号,但其上升时间非零,这样的信号近似于一个斜坡。

假设 $V_{tn}+|V_{tp}|<V_{DD}$,输入电压 $V_{in}$ 由 0 上升到 $V_{DD}$,输出电压 $V_{out}$ 会经历三个阶段:

阶段一 $0<V_{in}<V_{tn}$:nMOS OFF,pMOS ON

$$

V_{out}=V_{DD}

$$

阶段二 $V_{tn}<V_{in}<V_{DD}-|V_{tp}|$:nMOS ON, pMOS ON(互相对抗)

$$

\frac{dV_{out}}{dt}=\frac{I_{dsp1}-I_{dsn1}}{C_{load}}

$$

阶段三 $V_{DD}-|V_{tp}|<V_{in}<V_{DD}$:nMOS ON, pMOS OFF

$$

\frac{dV_{out}}{dt}=\frac{-I_{dsn1}}{C_{load}}

$$

与阶跃上升信号相比,斜坡上升信号的传播延迟(见下一节)增大。这是因为在第二阶段中,nMOS 一开始并没有完全导通,且它还必须与 pMOS 对抗。